关于quartus的FFT IP核的一些整理

软件版本使用quartus 11.0 sp1 当然11.0也能打开并仿真。

整理的原理图如图所示,原理图不能用于modelsim仿真,所以还需要将原理图转化为Verilog语言文件,file - creat/update—>creat HDL file form current file.便可生成原理图对应的.v文件,并将其作为顶层文件。

其中fft核的生成过程不再赘述,主要是fft_ctrl.v模块的设计,其实也很简单,有一点需要注意,需要根据fft核的输出信号sink_ready信号判断是否开始控制转换。

module fft_ctrl( input reset_n, input clk, input sink_ready, output reg sink_sop, output reg sink_eop, output reg sink_valid, output [7:0] data ); //reg[7:0] frame; reg[7:0] count,next_count; reg [2:0] current_state,next_state; // reg sink_sop,sink_eop,sink_valid; wire sink_sop_d,sink_eop_d,sink_valid_d; parameter idle =4'b000, go =4'b001, assert_eop =4'b010, wait_state =4'b100; always@(current_state,sink_ready,count) begin case(current_state) idle: begin next_count<=0; if(sink_ready==1) next_state<=go; else next_state<=idle; end go: begin if(count<62) begin next_state<=go; next_count<=count+1; end else begin next_state<=assert_eop; next_count<=count+1; end end assert_eop: begin next_count<=0; next_state<=wait_state; end wait_state: begin if(sink_ready==1) begin next_count<=0; next_state<=go; end else begin next_count<=count; next_state<=wait_state; end end endcase end assign data = count+7'd100; assign sink_sop_d = ((next_state==go) && (next_count==0))?1:0; assign sink_eop_d = (next_state==assert_eop)?1:0; assign sink_valid_d = ((next_state==go) || (next_state==assert_eop))?1:0; always@(negedge reset_n or posedge clk) begin if(reset_n==0) begin current_state<=idle; count<=0; sink_sop<=0; sink_eop<=0; sink_valid<=0; end else begin current_state<=next_state; count<=next_count; sink_sop<=sink_sop_d; sink_eop<=sink_eop_d; sink_valid<=sink_valid_d; end end endmodule

最后是testbench的编写:

`timescale 1 ps/ 1 ps module ifft_vlg_tst(); reg clk; reg rst_n; reg [1:0] sink_error; reg source_ready; // wires wire [7:0] rom_data; wire sink_eop; wire sink_ready; wire sink_sop; wire sink_valid; wire source_eop; wire [1:0] source_error; wire [5:0] source_exp; wire [7:0] source_imag; wire [7:0] source_real; wire source_sop; wire source_valid; // assign statements (if any) ifft i1 ( // port map - connection between master ports and signals/registers .clk(clk), .rom_data(rom_data), .rst_n(rst_n), .sink_eop(sink_eop), .sink_error(sink_error), .sink_ready(sink_ready), .sink_sop(sink_sop), .sink_valid(sink_valid), .source_eop(source_eop), .source_error(source_error), .source_exp(source_exp), .source_imag(source_imag), .source_ready(source_ready), .source_real(source_real), .source_sop(source_sop), .source_valid(source_valid) ); initial begin #1 $stop; sink_error = 2'b00; source_ready = 1'b1; rst_n = 0; #200 rst_n = 1; //the time of asset the rst_n must be long time end initial begin clk = 0; forever #5 clk = ~clk; end

endmodule

其中testbech的有一个地方需要特别注意,

#200 rst_n = 1;

一定要延时足够长的时间,才可以!不然会出现转换数据不连续的结果,原因大概是因为fft核需要一段时间初始化的原因吧

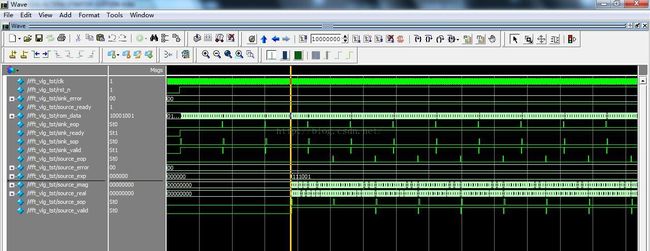

</pre><pre name="code" class="plain">modelsim仿真结果如图: