min pulse width 最小脉冲宽度

什么是min pulse width?

Min pulse width,也就是最小脉冲宽度,它是DRV检查的一种。Min pulse width用于检查时钟信号的波形是否处在一个合理的状态。时序单元对时钟的高电平和低电平的脉冲宽度有一定的要求,经过min pulse width检查可以获悉时钟信号的最小脉冲宽度是否满足了时序单元的要求。

为什么会出现min pulse width的问题?

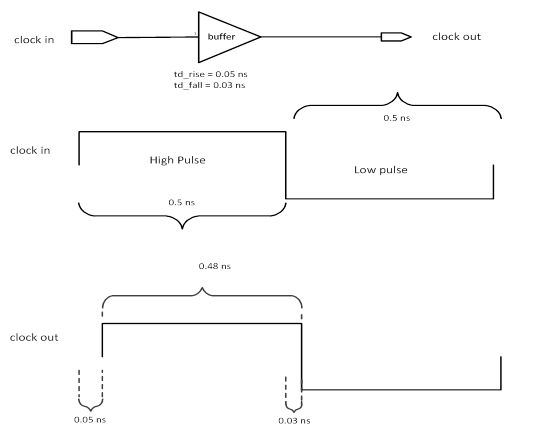

假设一个占空比为50%的时钟穿过一个buffer,假设上升的延时大于下降的延时,则经过buffer后的时钟高电平宽度会缩小。当经过多个这种单元后,高电平的宽度会进一步减小。当减小到一定程度时,就会出现min pulse width的违例。

如何检查min pulse width?

不同时序单元对min pulse width的要求不同,EDA工具通过查找单元库文件来获取min pulse width的阈值。

在库文件中,min pulse width是一个查找表,其阈值与transition直接相关。

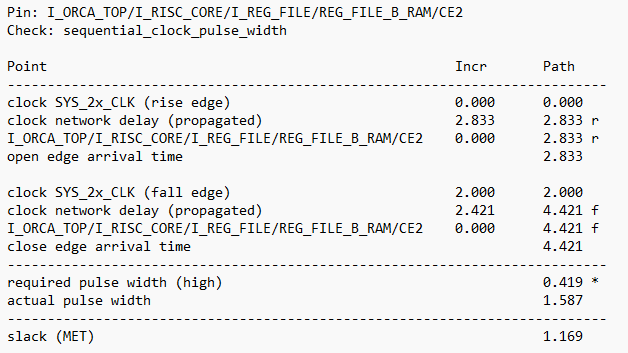

在PrimeTime中,可以通过report_min_pulse_width命令来获取min pulse width的结果。

例如:report_min_pulse_width -verbose I_ORCA_TOP/I_RISC_CORE/I_REG_FILE/REG_FILE_B_RAM/CE2

如何修复min pulse width?

首先,检查是否有比较大的transition。减小transition有利于min pulse width。

其次,检查是否有不合理的阈值电压的单元。一般时钟路劲需要用低阈值电压(如ULVT)的单元,而且需要保证阈值电压的一致性,也就是时钟路径上需要用相同的阈值电压的单元。

然后,检查时钟路径上的单元是否都采用了时钟专用的单元。一般单元库名称中带有CK关键字的是时钟专用的单元,这样的单元具有更好的上升和下降一致性。

然后,检查是否有串扰,也就是SI,消除或者减少串扰引起的延时。

然后,检查时钟路径是否有绕远。将路径做到最短,也有利于min pulse width。

然后,将buffer换成inverter也对min pulse width有一定的帮助,因为inverter具有更好的上升和下降一致性。更聪明的方式是,在buffer chain的头尾各加一个inverter,当然前提是保证不改变功能,也就是buffer chain的扇出需要全都是1。这样做有效的原理是,将对上升或下降沿有害的偏斜转化为了有用的偏斜,这类似于setup timing中的useful skew,因此前提是有足够的margin。也就是,在修high时需要保证low有足够magrin,在修low时,需要保证high有足够的margin。

最后,放松标准。是否一定要6 sigma?能否放松到3 sigma?

扩展阅读

1.为什么报告中会有clock uncertainty?

min pulse width 都是半周期检查,因此需要加入clock uncertainty来考虑jitter等因素的影响。

2.可以在data或reset pin上做min pulse width检查吗?

可以的,不过需要相关的设置。

首先,需要在想要检查的位置定义一个时钟;然后,将此时钟设置为propagated clock,也就是将时钟展开;最后,通过report_min_pulse_width检查min pulse width的结果。

3.min pulse width是否考虑CRPR?

首先,min pulse width的检查路径是相同的路径,不过是反相的。PrimeTime对反相的CRPR处理由变量timing_clock_reconvergence_pessimism 控制。当设为normal时,会考虑CRPR上升和下降沿的最小值;当设为same_transition时,不会考虑CRPR。建议设为same_transition,这样更加严格。

4.CTS之前是否可以检查min pulse width?

可以的,不过结果并不准确。CTS之前检查min pulse width需要在时序单元的时钟端设置一个合理的transition(这个值很重要,会影响结果),此时检查min pulse width的意义在于,检验存储器RAM是否能满足min pulse width。如果CTS之前不能满足min pulse with,那PR(布局布线)后很可能依然不能满足,尽早更换RAM,免得返工。

5.min pulse width需要考虑串扰(SI)的影响吗?

需要的,在考虑串扰(SI)的情况下,依然需要满足min pulse width。

6.已经使用了很快的RAM了,为什么还是有很大的min pulse width违例?

RAM的min pulse width查找表选择,和case的状态有关。检查某些pin是否丢了case value。

7. 什么是 sequential_clock_pulse_width 和 clock_tree_pulse_width ?

min pulse width 主要分为两种,分别为sequential_clock_pulse_width 和 clock_tree_pulse_width。sequential_clock_pulse_width 是针对时序单元的时钟端的min pulse width检查;而clock_tree_pulse_width 是针对时钟路径上的组合逻辑单元的min pulse width检查。