《低功耗方法学》翻译——第六章:功率门控的架构问题

第六章:功率门控的架构问题

本章讨论了植入功率门控设计中涉及的一些架构问题。特别地,它解决了分区、层次结构和多个功率门控域的问题。

6.1 层次化结构和功率门控

芯片架构的可扩展方法是有价值的,因为今天在芯片上的系统设计经常在随后的产品生成中成为一个更大的芯片中的一个组件。

为了支持这种可移植性,必须在功率域级别上强制执行模块边界。也就是说,一个给定的模块应该属于一个单个功率域,而不是跨多个域进行拆分。一些工具和流程通过将RTL进程分配到功率域来支持RTL进程,但这导致了更复杂的实现和分析。电源门控块边界的清晰可见性是拥有一个清晰的、自上而下的实现和验证流程的关键。

虽然理论上可以将电源门控模块任意嵌套在电源门控子系统中,而这些网关子系统又嵌套在共享的交换电源轨道上,但不创建多个级别的电源开关结构有相当大的好处。如第11章所述,电源门控具有侵入性,并增加了一些电压降和性能下降。级联的多次电压降会导致不可接受的延迟增加。

即使设计在架构级别上被表示为分层,但如果在实现时映射到单个级别的电源门控,实现也会得到改进。请考虑一下图6-1中所示的示例。CPU在概念上有所有的核心逻辑功率门控,其中有许多功能单元,每个功能单元都可以独立断电——在这种情况下,有一个乘法累加单元和一个向量浮动点单元:

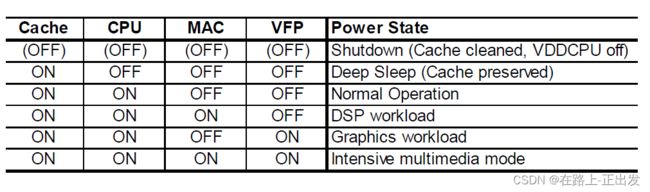

操作模式如下表所述:

从实现的角度来看,开关结构是扁平化的,如图6-2所示。不存在MAC或VFP功能单元在没有CPU核心通电的情况下打开的情况。因此,开关机控制语义被调整为 与 控制术语,而不是级联开关元件。

功率模式表包含了对嵌入的功率门控功能单元的显式控制。

建议:

- 将电源门控区域映射到显式的模块边界

- 当划分分层电源门控设计时,确保电源门控控制项可以映射回扁平的开关结构

避坑:

- 避免控制信号通过电源门控或电源关闭区域传递到没有与第一个区域进行分层开关的其他电源区域。

- 避免过细的功率门控粒度,除非绝对需要激进的泄漏功率管理。每个接口都增加了实现和验证方面的挑战,并使系统级生产测试的挑战变得复杂。

- 避免超过一个或两个的级别的功率门控系统。

6.2 功率网络和对应的控制

在基于处理器的 SOC 的设计中,CPU 系统很可能引入大量的电源线网:

- 一个独立的电源轨道到整个缓存的CPU子系统-长期“休眠”的操作模式允许CPU完全关闭缓存子系统。

- CPU逻辑的电源门控电源,支持短期泄漏节省模式,可以保留缓存内存,但所有泄漏的标准单元逻辑在本地关闭。

- 可选地,来自非电源门控轨道的某种形式的常开保持电源。这是为了支持设计的标准单元部分中的状态保留寄存器。

- 为隔离单元提供始终接通的电源。

- 针对电源门控控制器和所有电源控制信号上的缓冲器的非电源门控电源:电源开关控制、保持控制和隔离控制。

- 一个 SOC 级始终开启的电源,以控制外部导轨开关握手与电源。

图6-3说明了具有独立的“VDDCPU”和始终接通的“VDDSOC”的公共VSS接地连接的供电网络;在本例中,电源门控标准单元区域具有非门控状态保留电源,表示电源门控区域内的有效供电轨道:

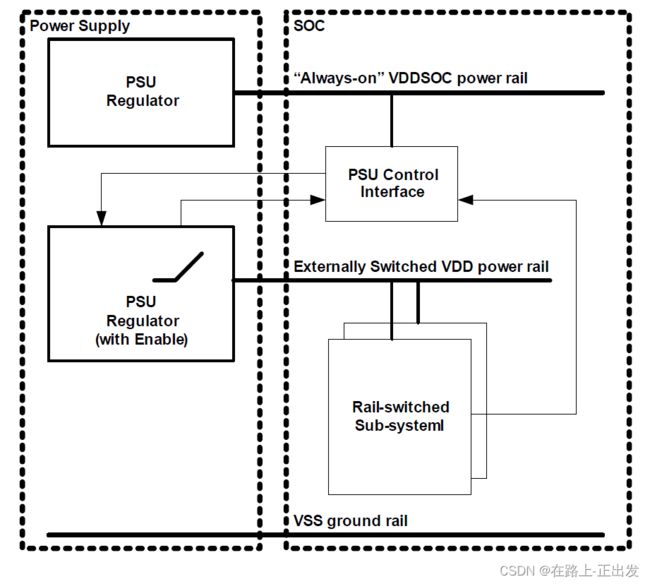

6.2.1 外部供电轨道开关

外部电源轨道开关提供了最好的长期泄漏功率节约-但引入了一个显著的开启延迟,以允许电压调节稳定并固定在规格范围内。

通常只有少数几个电压轨道可以在外部切换;每个电源导致增加(外部)调节器的成本和电路板上的区域,包括实现开关模式电源所需的电感器和电容器。每条供电轨也需要片上电力分配,增加面积成本,使电力规划和物理版图规划复杂化。大多数 SOC 已经有至少三个供电轨:

- IO供电(至少一个1.8/2.5/3.3V,可能还有几个取决于应用需求

- “始终上电”的SOC核心轨道(技术相关逻辑和内部存储电源轨道)

- PLL干净的模拟电源轨道。

- 一个可选的“保持活跃”电压供应到实时时钟

增加两个或三个以上的外部开关电源导轨会大大增加最终产品的复杂性和成本。

通常,芯片和电路板的共享地面/VSS连接方式最适合外部电源导轨开关。虽然IO垫环和芯片核心通常有独立的VSS引脚,以从逻辑和内存消除同时开关活动的输出,但它们通常基于电路板到一个共享的“0伏”地平面。将任何其他电源作为相对于共地的开关正电源,可减少增加电源门控时的复杂性。

外部电源轨道开关会在唤醒事件上造成重大延迟——从几十微秒到毫秒甚至更长时间。更快的供电开关时间并不一定是可取的。在断电子系统中,给所有电容节点重新充电的过冲电流导致噪声注入到芯片的其他(已上电)区域。在共享地面系统中产生的“地面弹跳(地弹效应)”可能会引入一些问题,直到在设计流程的实现和分析阶段的后期才能量化这些问题。

将这些延迟转换为RTL级别的时钟周期个数并不简单。通常,这些时钟应被抑制,直到开关供电轨道稳定并在指定的允许范围内。对于一个运行在数百兆赫兹区域的设计,这可能相当于成千上万个时钟周期。实际的延迟高度依赖于电源技术(在一个产品中可能必须是多来源的)。

当引入动态电压缩放时(第9章),必须分离电源导轨。例如,还可能非常希望提供大量自主供电的存储器,它们可以切换到中间RAM保留操作条件。这将在第13章中进一步讨论。

建议:

- 最小化外部开关独立电源轨道的数量——考虑到相关的额外电源面积成本和片上功率分配,每一条电源轨道都与最终产品需求相契合。

- 对于外部开关轨,最好切换(正)电源轨,并保持接地。

- 在实现电压缩放的系统中,必须在电压缩放区域提供独立的轨道。

陷阱:

- 为显著的外部电源轨道切换时间而设计:在唤醒时必须考虑数千或数万个时钟周期延迟,并将取决于外部PSU的规格。

- 尽管从系统设计的角度来看,多个电源轨道看起来很优雅,但它们在生产中引入了验证和部署方面的挑战。独立的供电导轨具有独立的电压控制调节器,与接口处的逻辑供电相比独立的导轨在激活、等待或停止时表现出显著不同的负载调节特性。

6.2.2 片上功率门控

芯片上的电源门控比芯片外的电源轨道门控要快得多。电源控制区域越小,电源的开关速度可以越快。供电一个小电源门控区域的电流要求比大模块小得多。但是必须通过时间预算来管理最小化功率门控瞬变(电压和电流)和噪声注入的其他逻辑和内存。

因此,事实上很好理解对于非常小的区域仅需要几个时钟周期就可以实现电源门控,对于更大的门控区域则需要几十甚至数百个时钟周期实现电源门控。同时打开大量小的电源门控区域不会比给一个大模块供电更容易,而且可能会导致一个更复杂的电源控制器。

由于开关晶体管结构的性质,功率门控对性能和面积都有影响,这将会在后续章节讨论。这些限制影响了系统体系结构和设计目标。

建议:

- 针对依赖于技术的电源门控时间的设计:取决于开关控制的面积和开关结构控制特性,可能需要将数十或数百个时钟周期延迟考虑到唤醒时间中。

- 设计为“等待状态”跨边界,其中有动态功率门控的功能单元,这样与实现相关的延迟时间可以模糊地管理和设置延迟约束。

陷阱:

- 每条电力门控轨道都引入了验证和测试挑战,因此需要仔细证明电力门控区域的数量,并将其纳入项目时间尺度。

6.3 电源状态表和始终通电区域

当处理多个电源门控电源域时,电源布线可以变成复用。特别是,“always-on”的概念变得不那么清楚了。图6-4显示了三个电源域,每个电源域都是电源门控的。

如果电源域B始终打开,则没有问题。但是,如果域B关闭,而域A和C通电,则会出现问题:由于B中的缓冲器断电,从A到C的输出被破坏。在这种情况下,我们将不得不将电源从另一个始终打开的电源传送到B中的缓冲器。我们可以使用A中的隔离电源(因为即使A断电也保持打开),也可以使用C的电源。

另一方面,如果我们知道无论何时B断电,C也被关闭,我们不需要为B提供特殊的供电。在这种情况下,我们认为B“相对始终打开(relatively always-on)”,也就是说,相对于域C始终有电。

因此,我们最终可能会得到一些相当复杂的电源布线规则,这取决于不同块之间的电源门控关系。

UPF为系统架构师提供了一种简洁的设置方法,可以将这些电源门控依赖规则给到实现工具。

create_pst 和 add_pst_state 命令允许我们创建一个电源状态表,可用于指定不同的电源供应网络之间的关系。看有关这些命令的描述,请见附录B。

第六章翻译结束~