SOPC之NiosⅡ系统(二)

常用NIOS Ⅱ组件概括

目录

1.时钟组件

2.Nios Ⅱ处理器

2.1 Main

2.2 Vector

2.3 Caches and Memory Interfaces

2.4 Arithmetic Instructions

2.5 JTAG Debug

3.RAM组件

4.System ID组件

5.JTAG UART组件

6.PIO组件

6.1 基础设置(Basic Settings)

6.2 输出寄存器(Output register)

6.3 边沿捕获寄存器(Edge capture register)

6.4 中断(Interrupt)

6.4.1 电平触发 IRO

6.4.2 边沿触发IRO

1.时钟组件

当打开Platform Designer就会默认添加了一个CLOCK组件,通过双击clk_0可以进行参数设置

时钟频率(Clock frequency)默认为50000000Hz,即50MHz,那么在Qsys系统的顶层会引出一个clock输入信号,在 FPGA 中就必须输人一个 50MHz 的时钟信号与之相连接。

时钟频率已知(Clockfrequency is known)默认勾选

复位同步边沿(Reset synchronous edges)有 None,Both 和Deassert三个选项,这些设置主要与复位和时钟的同步或异步控制机制有关。若没有特殊要求,可以不用设置。

2.Nios Ⅱ处理器

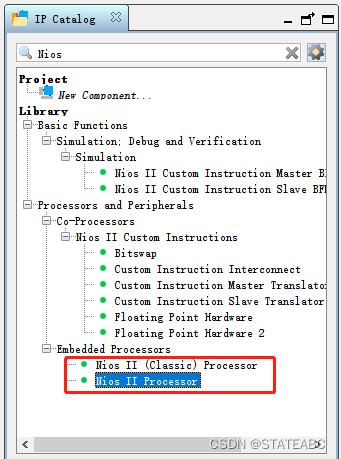

在IP Catalog中搜索Nios可以找到,双击添加Nios Ⅱ Processor组件

(14.0版本之前叫Nios Ⅱ(Classic)Processor、14.0版本之后叫Nios Ⅱ Processor)

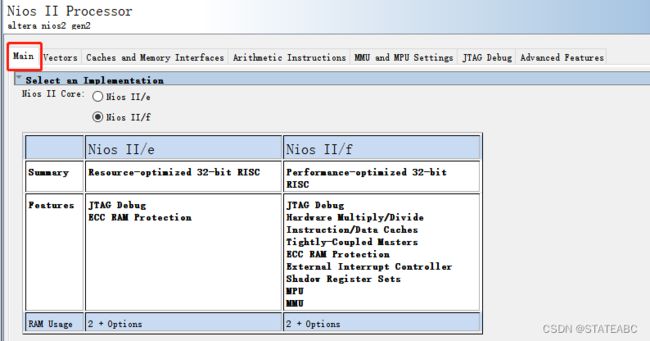

2.1 Main

添加后会有类型选择Nios II/f(快速型,消耗资源最高,性能最强)Nios II/e(经济型,消耗资源最少,性能最低)

2.2 Vector

Nios Ⅱ还需要在添加完存储器组件后设置复位向量和异常地址向量

复位向量存储器(Reset vector memory)用于设置CPU复位后从什么地方启动

异常向量存储器(Exception vector memory)用于存放CPU处理异常时间的代码,例如中断代码。该向量常指向于一个低延迟存储器,如SDRAM、SRAM、或者片上存储器(On Chip RAM)

快速TLB命中异常向量(Fast TLB Miss Exception Vector)主要与MMU协作,管理存储器

2.3 Caches and Memory Interfaces

主要设置CPU的数据和指令缓存部件

指令缓存(Instruction cache)用于缓存NIOS II处理器的各种指令,以提高 CPU 的运行效率。该缓存的大小从 512 字节到 64K 字节用户可自定义设置,也可以不使用指令缓存。

当选择不使用指令缓存时,NIOS II处理器的指令总线将会被移除,因此必须要包含一个紧耦合型指令存储器(tightly-coupled instruction memory)。

数据缓存(Data cache)用于存放数据,Datacache数据缓存选项用于指定缓存的大小。该缓存的大小从 512 字节到 64K 字节用户可自定义设置,也可以不使用指令缓存。

指令缓存和数据缓存在刚开始接触NIOS II处理器时使用默认设置即可。

2.4 Arithmetic Instructions

用来设置NIOS II处理器实现算术指的方式,可以通过选择Divide Hardware来设置NIOS II处理器是否支持硬件除法运算,也可以选择乘法、移位等运算的实现方式。

2.5 JTAG Debug

该模块为了方便调试,但要占用较多逻辑资源,调试完毕后可取消勾选。

JTAG调试模块根据功能的不同可设置是否使用硬件断点,使用数据触发,跟踪类型和跟踪存储等。

3.RAM组件

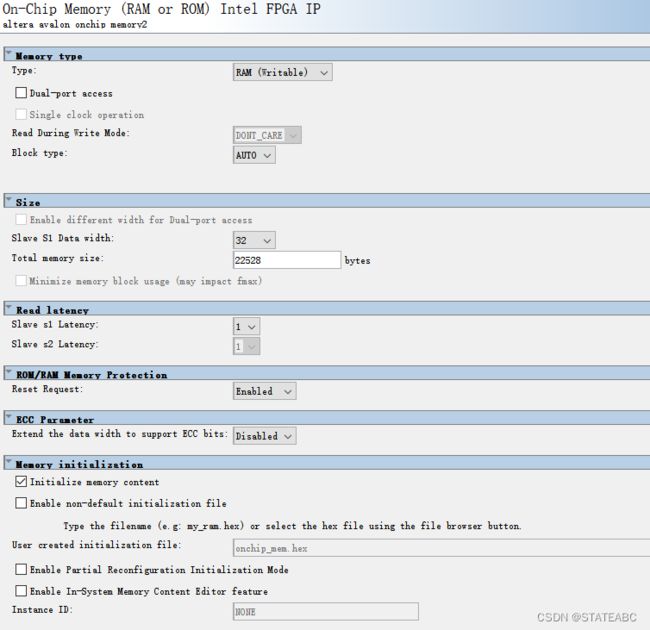

在IP Catalog中搜索On-chip添加On-chip Memory(RAM or ROM)组件

存储器类型(Memory Type)中Type有RAM(Writable)和ROM(Read-only)两个选项

Size中设定存储器数据位宽(Data width)为32位,存储量大小(Total memorysize)为 22528B(即 22KB)。其他设置使用系统默认设置。

4.System ID组件

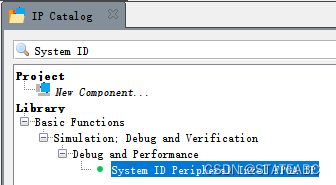

在IP Catalog中搜索System ID添加System ID Peripheral Intel FPGA IP组件

System ID是Nios Ⅱ处理器的唯一识别号,用于确认当前运行的程序和 FPGA 中内嵌的 Nios Ⅱ处理器是否相匹配。

System ID的值为32位,在Qsys中添加该组件时设置。在弹出的 System ID组件设置页面中,可以设置这个32位ID值为0x1223344

5.JTAG UART组件

在IP Catalog中搜索JTAG UART添加JTAG UART Intel FPGA IP组件

JTAG UART使用FPGA 的JTAG 接口协议实现PC和FPGA内部Nios Ⅱ处理器之间串行字符串的传输

在JTAG UART 组件设置页面中,为了降低这个外设所要用到的缓存FIFO对存储器的需求,设置 Write 和 Read FIFO 的存储量为16B,并且选上Construct using registers instead of memory blocks,表示不使用FPGA片内存储器,而是使用FPGA的逻辑来实现 FIFO。

6.PIO组件

在IP Catalog中搜索PIO添加PIO(Parallel I/O) Intel FPGA IP组件

6.1 基础设置(Basic Settings)

设置PIO端口的数据位宽(Width,1-32bits,因为最高提供32个I/O端口)

设置PIO端口方向(Direction)

Bidirectional(tristate) ports,每个PIO位使用一个引脚来驱动和捕获数据,可单独设定每个引脚方向

Input port only,PIO端口只能捕获输入数据

Output port only,PIO端口只能驱动输出

Both input and output ports(InOut),输入和输出端口总线独立,同时生成输入和输出端口

设置端口复位值(Output Port Reset Value)可以确定输出端口的复位值,有效值的长度取决于端口宽度

6.2 输出寄存器(Output register)

6.3 边沿捕获寄存器(Edge capture register)

要检测的边沿种类

Rising Edge 上升沿:

Falling Edge 下降沿:

Any Edge 上升或下降沿。

选择了Enable bit-clearing for edge capture register选项后,给edge capture 寄存器单独的位写1清中断

6.4 中断(Interrupt)

6.4.1 电平触发 IRO

(2) 在Interrupt项中,选中GenerateIRQ选项

(4) 使能中断。在硬件设置完成后,需要在软件中给中断屏蔽寄存器 (interruptmask Register) 写1。

(2) 当PIO IP核某一个输入端口满足IRQ触发条件,PIO IP核发出IRQ后,程序开始处理中断函数假如此时输入端口一直满足IRO触发条件,那么程序在处理完中断函数后会再次进入中断函数接着运行直到触发条件不存在了,程序才能在处理完中断函数后回到主函数。

(3) 若程序中有复数个中断函数,且中断函数之间还有优先级的区别,就可能发生这样的情况:主程序正在处理某一个中断函数,这时突然触发一个优先级更高的IRO,那么主程序会从当前处理的中断函数跳到优先级更高的中断函数。

6.4.2 边沿触发IRO

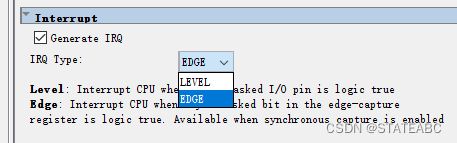

产生边沿触发IRO需要的条件

(1) 首先PIO核的端口需要是Input的端口

(2) 在Edge capure register(边沿捕获寄存器)栏选中Synchronously capture选项。此时可以在 Edge type一栏选择触发电平,里面的选项有 RISING (上升沿)、FALLING (下降沿)、ANY(任意边沿)。在 Edgcapure register 栏还有 enable bit-clearing for edge capture register 选项。选择了 enable bit-clearing for edgccapture register 选项后,给 edge capture 寄存器单独的位写1 清中断:若是没有选择 nable bit-clearing foredge capture register 选项,则是写任意数清中断。每触发一次边沿类型的IRQ 后,需要给 edge capture 寄存器写 1清一次中断,否则 PIO IP 核会一直输IRQ。(3) 在 PIO IP 核中加入IRQ 这个功能,也就是在 nterrupt 项中,选中 Generate IRQ 这一选项 (4) 选中边沿触发选项,即在 IRQ type (IRQ类型)中选中 EDGE。

(5) 使能中断。在硬件设置完成后,需要在软件中给中断屏蔽寄存器 (interruptmask Register) 写1

(3) 若程序中有多个中断函数,且中断函数之间还有优先级的区别,就可能发生这样的情况:主程序正在处理某一个中断函数,这时突然触发一个优先级更高的IRO,那么主程序会从当前处理的中断函数跳到优先级更高的中断函数。

参考文献:特权同学《勇敢的芯-伴你玩转NIOS Ⅱ》、正点原子《开拓者Nios Ⅱ开发指南》