【Verilog HDL学习之路】第二章 Verilog HDL的设计方法学——层次建模

2 Verilog HDL的设计方法学——层次建模

- 重要的思想:

在语文教学中,应该先掌握核心方法论,再用正确的方法论去做题目,这样能够逐渐加深对于方法论的理解,做题的速度和准确率也会越来越高。 - 在Verilog HDL中,该思想同样适用,在编程,软件开发也一样如此

2.1 设计方法学——层次建模

2.1.1 方法理论

- 自上而下设计方法

设计者先设计出顶层模块,然后将其拆解,分析出其内部模块,再进一步为更小的、已知的功能单元。用流程图可以进行如下表示

- 自下而上的设计方法

设计者使用功能确定是小的功能单元,组合成大的功能单元,然后逐渐增大,流程图即上面的箭头反向

2.1.2 实际应用

在实际使用设计方法学的过程中,往往采用二者结合的方式,程序员一边设计顶层的架构,一边将小模块组合成大模块,上下同时进行,然后进行对接。

实际的流程往往是这个样子的

这个过程中,对于小单元的实现,是自下而上的,对于整体架构的实现,是自上而下的。

当然,其实这样的流程过于抽象,并且也不是唯一的,我们看后面的实例部分来深入理解思想即可,大可不必生搬硬套。

2.2 应用层次建模思想设计Verilog HDL程序

具体内容请参考书籍《Verilog HDL:A Guide to Design and Synthesis》(Second Edition)

先来阐述核心概念:

- 模块与模块实例

- 设计块与激励块

2.2.1 模块与模块实例

对于模块与模块实例的关系,和C++中模板与模板实例的关系是类似的

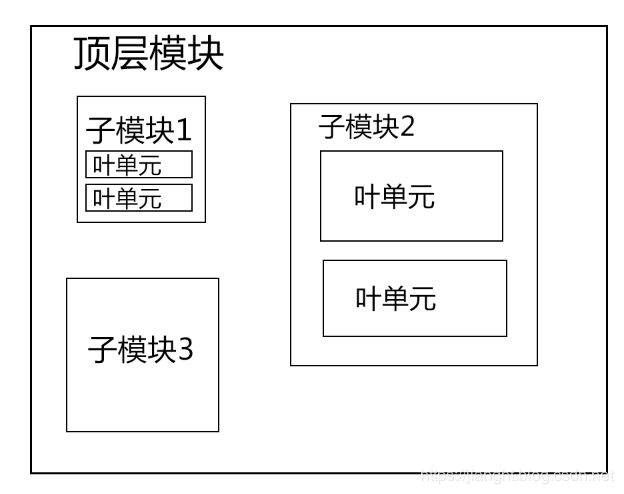

在Verilog HDL中,模块是基本功能单元,它可以是

- 叶单元

- 子模块

- 顶层模块

在更高级的模块中,可以调用低级模块实例来构建,也有了一条重要的原则:

- 下级模块实例,被调用,来构建上级模块

总而言之,Verilog的核心设计,是由模块构成的,不同等级的模块通过模块实例进行相互调用来建立联系

每一个模块,都是一个有接口,有功能,但是内部细节不可见的科技黑箱

每一个模块实例,都是模块的副本,可以被它的上级模块调用

2.2.2 设计块与激励块

- 设计块就是2.2.1中构建的最上级的模块,即顶层模块

- 激励块就是用来验证设计块的正确性

问题:什么是“激励”?

先来举一个类似的例子,在物理电路实验中,我们连接好电路,然后给他加上电源通电,验证电路是否连接正确。

在Verilog设计中,我们的“设计块”就是电路,“激励块”就是电源,“仿真测试”就是通电。这样的类比应该非常清晰明确了,再画个表格对比。

| Verilog HDL | 电路实验 |

|---|---|

| 设计块 | 电路 |

| 激励块 | 电源 |

| 仿真测试 | 电路通电 |

激励块的作用:

给设计块加上具备指定特征的信号,来测试设计块的正确性和效率

激励块的两种设计模式:

- 激励块中调用设计块实例,直接接入信号驱动设计块

- 生成一个新的“虚拟的”顶层模块,调用激励块实例和设计块实例,让二者接口进行交互,通过信号传递间接驱动设计块

举个例子你就明白了

- 方式一:手动点火来引爆炸药

- 方式二:使用引爆器引爆炸药

2.2.3 使用规则

- 模块、模块实例和激励块的命名,必须是唯一的,不能重名

- 模块不能嵌套定义,但是模块内部可以进行其他模块的声明或调用其他模块实例

- 模块由module开始,endmodule结束

2.2.4 示例

2.3 思考:层次建模在Verilog与C/C++应用的区别

层次建模的思想,一直都应该存在,但是在具体实现中,Verilog设计使用自上而下的设计是可能的,因为模块相对简单,接口相对确定,只需要设置好接口,知道需要的模块和功能即可。

但是对于高级语言来说,自上而下的在纸上设计框架是可以的,具体实现并不能这样的做,因为它的低层框架同样是非常复杂的,并不能直接提前设计好,尤其是对于大框架嵌套小框架的情况,一定要先设计好小框架,再完成大框架,也就是自上而下地设计,自下而上地实现。

对于并行的中层框架来说,实现顺序也需要按照执行顺序来编写。

2.4 疑问解答

对于第一章提到的问题,现在可以解答了。【Verilog HDL学习之路】第一章 Verilog HDL 数字设计总论

问题1:对于过程“RTL级描述描述–>门级网表”,门级网表等同于门级描述吗?

问题2:行为级综合工具的出现允许Verilog HDL进行行为级描述,那么它是可以将行为级描述转换为RTL级描述吗?

回答以上两个问题,Verilog HDL的设计者可以使用四种抽象层次对模块进行描述,最终通过综合工具后,一般生成的是门级结构的描述

另外补充一点,RTL级描述,通常指的是能够被逻辑综合工具接受的行为级描述和数据流级描述的混合描述