时钟信号

1、同步电路与异步电路

1.对于比较严格的定义:一个电路是同步电路,需要满足以下条件:

(1)每一个电路元件是寄存器或者组合电路

(2)至少有一个电路元件是寄存器

(3)所有寄存器接收同一个时钟电路

(4)若有环路,则环路至少包含一个寄存器

2、对于不算很严格的同步电路定义有:

(1)所有时钟的时钟来自同一个时钟源:比如下面的(分频电路)

CLKA、CLKC、CLKD、CLKE都是由300M这个时钟源分频而来,因此这个系统属于同步电路系统。

(2)当不是来自同一个时钟源时,只要CLOCK的周期有倍数关系并且相互之间的相位关系是固定的就可以算同步电路,比如,电路中用了10ns、5ns、2.5ns三个时钟,这三个时钟不是由同一个时钟源分频来的,但是这三个时钟的周期有倍数关系并且相位关系固定:10ns是5ns的2倍,是2.5ns的4倍,之间是整数倍关系,相位关系是固定的,因此也算是同步电路。

clcok之间没有倍数关系或者相互之间的相位关系不是固定的,比如电路中的5ns、3ns两个CLOCK,这两个时钟不是来自同一个时钟源,两者之间没有周期关系,因此是异步电路。

同步电路是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路。同步时序逻辑电路的特点是各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲带来时,电路的状态才能改变,改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x有无变化,状态表中的每个状态都是稳定的。

2、时钟/时钟树的属性

一般的时钟,指的是全局时钟,全局时钟在芯片中的体现形式是时钟树。

时钟树,是由许多缓冲单元(buffer cell)平衡搭建的时钟网状结构,如下图:

实际的时钟除了周期/频率、相位、沿、电平属性外,还有其他属性,也就是说:不是下面这样子规整的:

![]()

时钟有以下属性:

(1)时钟的偏移(skew): 时钟分支信号在到达寄存器的时钟端口的过程中,都存在有线网等延时,到达寄存器时钟端口的时钟信号存在有相位差,不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew)。

时钟偏移与时钟频率并没有直接关系,skew与时钟线的长度及被时钟线驱动的时序单元的负载电容个数有关。

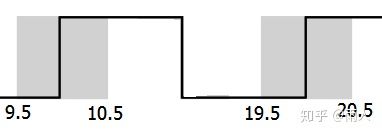

(2)时钟抖动(jitter): 相对于理想时钟沿,实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,如下图所示:

时钟的抖动可以分为随机抖动(Random jitter)和固有抖动(Deterministic jitter)。

随机抖动的来源为热噪声、shot noise和flick noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL工艺的PLL比TTL和CMOS工艺的PLL有更小的随机抖动。

固定抖动的来源为:开关噪声源、串扰、电磁干扰等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB布局和布线。

即,jitter与时钟频率无直接关系。

时钟的偏移和时钟的抖动都会影响着时钟网络分支的延迟差异(相位差异),在Design Compiler中,用时钟的不确定性(uncertainly) 来表示这两种情况的影响。

(3)时钟的转换时间(transition): 时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是如下图那个样完全没有跳变时钟的,时钟沿的跳变时间就是时钟的转换时间。

![]()

![]()

时钟的转换时间与单元的延时时间(器件特性)还有电容负载有关。

(4)时钟的延时(latency): 时钟从时钟源(晶振)出发到触发器的时钟端口的延时,称为时钟的延时,包含时钟源延时(source latency)和时钟网络的延迟(network latency)。

时钟源延迟(clock sourcw latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟输入引脚)的传输时间。上图是3ns。

时钟网络延迟(clock network latency)是时钟信号从起定义端(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

3、内部时钟

在verilog代码中,使用内部产生的时钟,即用内部的一个信号充当另一个always块的时钟沿敏感列表,如下图所示:

这种内部时钟是不建议使用,一是因为产生内部时钟的逻辑是有延时的,导致A_clk产生也会有延时,Data与A_clk就会有延时,就会有亚稳态的出现。另一个就是由触发器生成A_clk的驱动能力问题。

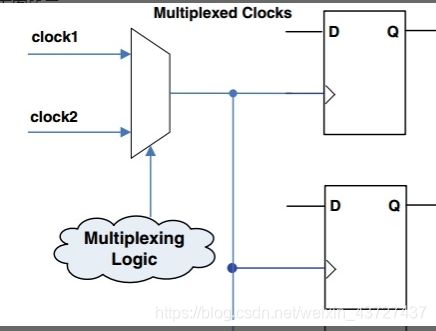

4、多路复用时钟

在一个系统中,很可能会用到多个时钟轮流驱动一些触发器,为了适应不同的数据速率要求,进行时钟切换,有时候为了节省功耗,也会把高速时钟切换到低速时钟,或者进行时钟休眠操作。

这样的时钟一般也会导致一些问题,比如时钟切换时导致后面驱动的寄存器建立时间不满足,当满足一定的条件时,这种多路复用器的时钟也是可以使用的,要满足的要求有:

(1)时钟复用电路一旦上电工作之后,就不要对复用逻辑进行更改,以便更改后产生不确定的错误。

(2)在测试的时候,设计电路绕过时钟多路逻辑来选择普通的时钟,也就是使用普通的时钟进行测试

(3)在时钟进行切换的时候,寄存器要处于复位的状态,以免在切换之后建立施加不够而进入亚稳态。

(4)在时钟切换的适合,可能会出现一些短暂的错误,但是这些错误对整个系统没有影响。

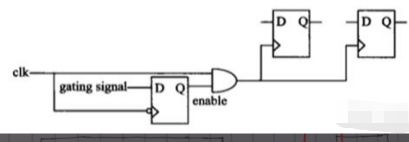

5、门控时钟

门控时钟就是在使能信号有效的时候,把时钟打开,使能信号无效的时候,时钟关闭。时钟关闭之后,它所驱动的寄存器就不会有翻转,因此也就是降低了动态功耗。

这样的门控时钟bug多,门控使能信号如果在时钟的高电平的时候开启或者关闭,就会导致产生的门控时钟高电平被截断,变成毛刺;门控使能信号对在时钟低电平时跳变对产生的门控时钟没有影响。

针对这情况,设置一种电路,让门控使能信号在通过这个逻辑电路之后,仅仅在时钟低电平的时候进行翻转,而在时钟高电平的时候,保持住。从而想到低电平触发的锁存器,使能信号通过低电平的锁存器之后,如果使能信号在高电平跳变,锁存器的输出信号是不会跳变的,电路图如下所示:

当门控使能信号是高电平有效的适合,也就是高电平打开门控时钟,低电平关闭门控时钟,使用上面的电路:低电平触发的锁存器+与门。

当门控使能信号是低电平有效的时候,要换成:高电平触发的锁存器+或门

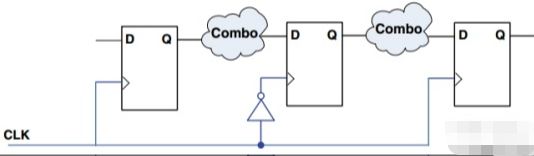

6、行波时钟

行波时钟,就是一个触发器的输出用作另一个触发器的时钟输入,经常用在异步计数器和分频电路设计中,如下图所示:

这种级联时钟(行波时钟)最容易造成时钟偏差,级数多了,很可能会影响其控制的触发器的建立时间和保持时间,使设计难度增大;转换的方法就是采用同步计数器。

7、双边沿时钟

双边沿时钟的系统是指在时钟的上升沿和下降沿都进行数据传输。

这样数据的传输速率就增加了一倍。DDR就是采用双边沿传输数据的技术。

(1)由于上下沿都用,要求时钟的质量很高,一般的时钟源很难达到,成本高。

(2)由于时钟的抖动等不确定因素的存在,容易使时钟的占空比发生改变,因此容易引起建立时间和保持时间的违例

(3)当使用双沿时钟之后,时钟的约束也变得复杂,当某处发生违规之后,违规的路径的查找难度比单沿时钟大。

(4)测试难度比较大,双沿电路的测试电路必定有别与单沿的测试电路。进行扫描测试时,上下沿的时钟先都得插入多路复用器进行选择。

8、Design Compiler中的时钟约束

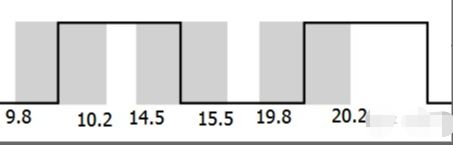

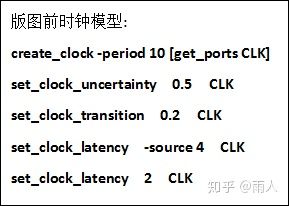

对实际的时钟进行建模/约束了,实际上就是对这几个属性进行设置。

在默认的情况下,逻辑综合时,即使一个时钟要驱动很多寄存器,DC也不会再时钟的连线上加时钟缓冲器(clock buffer)以加强驱动能力,时钟输入端直接连接到所有寄存器的时钟引脚,也就是说,对于高扇出(high fanout)的时钟连线,DC不会对它做设计规则检查和优化,如下图所示,在时钟连线上加时钟缓冲器或作时钟树的综合(clock tree synthesis )一般由后端(back end)工具完成,后端工具根据整个设计的物理布局(placement)数据,进行时钟树的综合。加入时钟缓冲器后,使整个时钟树满足Skew、latency和transition的目标。时钟树综合后的电路如下图:

右图是理想的,其延迟(latency)个时钟的偏差(skew)及转变时间(transition)默认值为0,。显然理想时钟网络与实际的情况不同,使用理想时钟网络将产生过于乐观的时间结果。为了能在综合时比较准确的描述时钟树,我们需要为实际的时钟树建模,使逻辑综合的结果能够与版图(layout)的结果相匹配。

使用下面的命令建立时钟那几个属性模型:

creat_clock、set_clcok_uncertainty、set_clock_latency、set_clock_transition分别进行时钟的周期、偏移、延时、转换约束。

时钟偏差的建模:

set_clock_uncertainty:对时钟的偏移和抖动进行建模,也就是对时钟的偏差进行建模,具体使用为:

假设时钟周期是10ns,时钟的建立偏差为0.5ns。用以下命令来定义进行约束:

creat_clock -period 10 [get_ports CLK]

set_clock_uncertainty -setup 0.5 [get_clocks CLK]

理想的时钟:

只对建立时间的偏差时钟建模:

如果对建立时间和保持时间都进行偏差建模,则有:

在默认情况下,“set_clcok_uncertainty”命令如果不加开关选项,“-setup”或“-hold”,那么该命令给时钟赋予相同的建立和保持偏差值。

这是一种对偏差建模的方式,也就是对建立时间和保守时间进行建模的方式:除此之外,还可以对时钟的上升沿和下降沿进行偏差建模,比如上升沿的偏差是0.2ns,下降沿的偏差是0.5ns,则有:

set_clock_uncertainty-rise 0.2 -fall 0.5 [get_clocks CLK]

一般情况下,只约束建立时间。

当对建立时间偏差建模之后,这时,时钟周期、时钟偏差和建立时间的关系如下图:

假设时钟周期是10ns,建立时间偏差是0.5ns,触发器的建立时间是0.2ns,这时钟从图中就可以看到,留给寄存器间的路径的余量就减少了,也就是说,对寄存器间的约束就变得更加严格了,寄存器的翻转延时、组合逻辑延时与线网延时等这些延时的和必须小于9.3ns,否则就违反了FF2发建立时间。

对保持时间,在未考虑时钟偏移之前,组合逻辑的延时要大于触发器的保持时间,当对时钟偏差建模之后,这是,时钟周期、时钟偏差和保持时间的关系如下所示:

时钟转换时间的建模

由于时钟并不是理想的方波,用set_clock_transition来模拟时钟的转换(transtion)时间。默认的上升转换时间从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。如果set_clock_transition命令中不加开关选项“-setup”或“-hold”,那么该命令给时钟赋予相同的上升和下降转换时间。一般情况下,我们只约束最大的转换时间,如最大转换是啊金是0.2ns。那么就加上-max选项

set_clock_transition - max 0.2 [get_clocks CLK]

时钟延迟的建模

时钟从时钟源出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),我们使用set_clcok_latency进行时钟延时的建模。一般情况下,我们把时钟源延迟(source latency)和时钟网络的延时(network latency)分开来,因为时钟源延时需要建模,是因为DC不知道延时有多爱大,对于时钟网络的延迟,DC在布局布线之前不知道,但是在布局布线这会就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就每页必须对是时钟网络继续延时,印象要把这两个延时分开约束。

先说布局布线之前:时钟周期为10ns,时钟源到芯片的时钟端口时间是3ns,时钟端口都内部触发器的时间是1ns,如下图所示,

那么就用下面的命令进行建模:

create_clock -period 10 [get-ports CLK]

set_clock_latency -source 3 [get_clocks CLK]

set_clock_latency 1 [get_clocks CLK]

通常情况下,我们约束最大的延时,也就是加上-max的选项,表示最大延时是多少(如set_clock_latency -source -max 3 [get_clocks CLK] 就是时钟源到芯片时钟端口最大的时间是3ns)。

布局布线之后:就可以计算实际的线网延时,就要使用

set_propagated_clock [ get_clocks CLK] 这个命令代替上面的

set_clock_latency 1 [get_clocks CLK] 这个命令。

时钟分配策略

时钟的分配从规划初始就应该考虑,也就是从系统层面上去考虑。不是等到后端设计时再考虑。

时钟分配的策略有:

(1)系统的时钟分配计划(主要是时钟树方案、各个模块的时钟频率等)

(2)时钟的最小延时(主要是根据系统运行的速度来定义最小的延时要求,这个与时钟分配计划应该是有重叠的地方);

(3)时钟缓冲(这个是考虑负载的问题,往往也是在设计时钟树时应该考虑的问题)

(4)消除时钟偏移(时钟偏移总是存在的,如何降到最小或使其达到预期的效果,也是要考虑的)

(5)门控时钟、软硬件协同设计等省电模式的考虑(这个需要具体问题具体分析了,还可以从低功耗设计的角度进行观察)。