数字电路实验二:FPGA实验箱内置单脉冲测试、数码管基础测试、74LS197产生8421码循环测试信号、实现8421码->格雷码译码器、3-8译码器、设计改进实现48译码器a段显示译码电路

数字电路实验报告二

- 实验环境与仪器

- 实验环境

实验时间:2022.11.10

地点:教学大楼A412

气温:22℃

- 实验仪器

示波器/逻辑分析仪 MSO5354

FPGA实验箱

元器件

目录

第一组数字电路实验报告二

参与者

一、 实验环境与仪器

1. 实验环境

2. 实验仪器

二、 实验内容

1.FPGA实验箱内置单脉冲测试——使用示波器LA测量单脉冲波形

2.FPGA实验箱内置数码管基础测试——测量两个4联装7段数码管管脚功能

3.74LS197产生8421码循环测试信号——连接产生4路二进制信号

4.设计实现8421码->格雷码译码器——设计4输入4输出译码器

5.3-8译码器测试与应用——观测74LS138特性

6. 数码管译码电路设计与实现—设计改进实现48译码器a段显示译码电路

总结和反思:

- 实验内容

1.FPGA实验箱内置单脉冲测试——使用示波器LA测量单脉冲波形

正脉冲:

负脉冲:

2.FPGA实验箱内置数码管基础测试——测量两个4联装7段数码管管脚功能

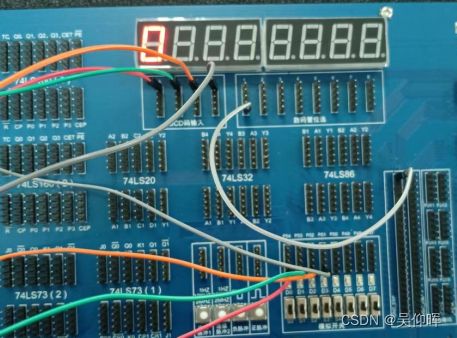

(1)如图连接电路,改变拨码开关设置为0000-1111时,依次显示‘0’、‘1’、‘2’、‘3’、‘4’、‘5’、‘6’、‘7’、‘8’、‘9’、‘10’、‘11’、‘12’、‘13’、‘14’、‘15’,以下为部分截图:

当拨码(BCD码输入)设置为0000时,显示‘0’:

当拨码(BCD码输入)设置为0101时,显示‘5’:

当拨码(BCD码输入)设置为0111时,显示‘7’:

当拨码(BCD码输入)设置为1001时,显示‘9’:

(2)拨码开关设置为1000,调整不同的位控端接GND,当数码管位选为1-8时,依次是第一个,第二个……第八个数码管亮,部分截图如下所示:

当接通第一位时:

当接通第二位时:

当接通第四位时:

当接通第七位时:

7段数码管的内容输入与位置控制的方法总结:数码管位控端第几位输入为低电平,则第几个数码管亮起;四位拨码开关输入四位二进制,相应的位置输出对应的十进制。

3.74LS197产生8421码循环测试信号——连接产生4路二进制信号

D0、D1、D2、D3分别对应74LS197的Q0、Q1、Q2、Q3的输出信号波形。

4.设计实现8421码->格雷码译码器——设计4输入4输出译码器

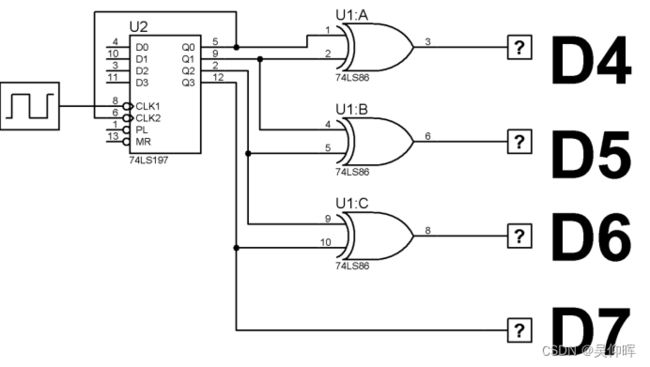

译码电路为:D7与D3输出一致,D6为将D3、D2接入74LS86芯片异或后的输出,D5为将D1、D2接入74LS86芯片异或后的输出,D4为将D1、D0接入74LS86芯片异或后的输出。其中,四输入为74ls197的Q0Q1Q2Q3,对应下图中的D0D1D2D3

电路示意图:

4输入4输出8个信号的波形如下,D3D2D1D0对应的格雷码是D7D6D5D4,四输入为74ls197的Q0Q1Q2Q3,对应下图中的D0D1D2D3:

格雷码的特点总结:连续的格雷码每次只有一位数发生变化;格雷码可由输入的最高位不变,其它位等于相应输入的位与高一位的数异或得到。

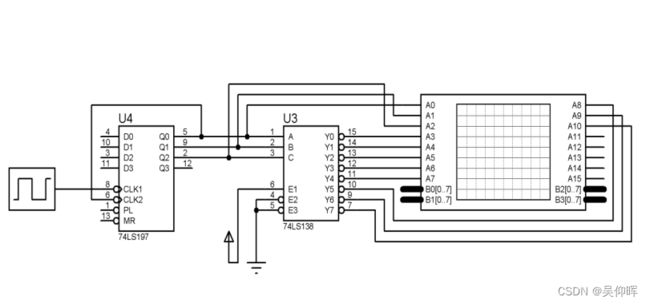

5.3-8译码器测试与应用——观测74LS138特性

3输入8输出信号波形如下,D3-D10为Y0-Y7的输出信号:

由波形图可看出:当CBA端输入的Q2Q1Q0为000,001,010,011……110,111时,输出端Y0,Y1,Y2,Y3……Y6,Y7依次输出为低电平。

2. 设计学号显示电路:先把Q3接到74LS138芯片低电平有效输入的任意一个选通端上(两个选一个),使得当Q2Q1Q0对应的二进制小于8时,74LS138有低电平有效输出,当Q2Q1Q0对应的二进制大于8时,两个选通端74LS138输入为高电平,输出全为高电平(无有效输出);接着将74LS197的输出端Q0、Q1、Q2、Q3分别接到4联装7段数码管的BCD码输入端的A、B、C、D上;再根据学号中的数字(0-7)和位置,把74LS138的对应的输出端接在数码管位选的对应位置上,如下图中将Y1接到2、4、5的位置上,从而令学号的第2、4、5位为1,Y2、Y3分别接到1、3的位置上,从而令学号的第1、3位分别为2、3等。当需要显示‘8’时,则将Q3通过74LS04芯片后再和Q2、Q1、Q0依次通过74LS32的输出接到需要输出8的数码管的位置上,则当Q3Q2Q1Q0为1000时,8显示。当需要显示‘9’时,则将Q3、Q2通过74LS04芯片后再和Q1、Q0依次通过74LS32的输出接到需要输出9的数码管的位置上,则当Q3Q2Q1Q0为1001时,9显示。电路示意如下:(21311139)其中实验箱的7段数码管相当于下图中的7段数码管加74LS48.

3. 学号显示如图所示:

4. 提升扫描显示效率的办法:

上面的实验实际是让74LS138在输入大于7之后停止工作,不输出有效电平,然后8和9用来逻辑门实现选择显示。

但是实际上,我们完全可以让74LS197在输出7之后(也就是输出8的时候)清零重新计数,这样就可以节省掉一段显示时间。那8和9该如何显示呢?其实思路很简单,8和9可以用其他数字的重叠来扫描显示!

从下面的数字真值表可以看出,对于数字8,我们不妨让0~7数字依次全部显示,扫描时就会在LED数码管重叠成显示数字8;

对于数字9,我们只要让没有左下那一竖的数字全部显示,也就是数字1 、3、 4、 5、 7依次全部显示,扫描时就会在LED数码管重叠成显示数字9。

对于其他数字,即74LS138扫描选择的1-7中,也有一些数字能用此方法增加某些笔画的扫描时间,提升扫描效率,比如数字7和4都有数字1的笔画。

5. 波形时序图上内容与位置对应的状态:

下面的D0D1D2对应74LS197的Q0Q1Q2,D3~D10对应数字0、1 、2 、3 、4 、5 、6 、7的选通。D13、D14对应8和9的选通。

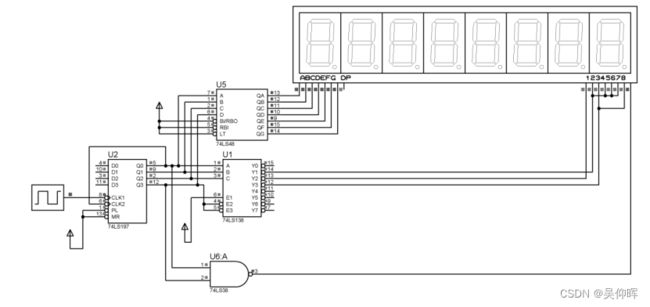

6. 数码管译码电路设计与实现—设计改进实现48译码器a段显示译码电路

实验设计与过程:

字符0~A的对应二进制和a段如下表(a段那一栏1表示显示,0表示不显示):

| 显示字符 |

对应二进制 |

a段 |

| 0 |

0000 |

1 |

| 1 |

0001 |

0 |

| 2 |

0010 |

1 |

| 3 |

0011 |

1 |

| 4 |

0100 |

0 |

| 5 |

0101 |

1 |

| 6 |

0110 |

1 |

| 7 |

0111 |

1 |

| 8 |

1000 |

1 |

| 9 |

1001 |

1 |

| A |

1010 |

1 |

| b |

1011 |

0 |

| C |

1100 |

1 |

| d |

1101 |

0 |

| E |

1110 |

1 |

| F |

1111 |

1 |

我们就根据这张表来设计改进48译码器在a段的显示,可以观察到1多而0少,所以以“0逻辑”来设计电路。

也就是在输入0001、0100、1011 、1101的时候a段显示。最直接的做法是用逻辑门直接搭建,不过在实验过程中,我们对1和4(0001和0100)用74LS138来实现,而b和d(1011和1101)则用逻辑门(非门和与非门,因为实验箱有4输入与非门,没有4输入与门)来实现,然后再用与门连接起来。示意电路图:

实验结果:

从下到上依次对应改进译码器的输入端ABCD(即197的Q0Q1Q2Q3输出),最上面就是改进74ls48译码器的a段输出。可以观察到a段输出只有在Q3Q2Q1Q0是0001、0100、1011 、1101才是低电平,其他为高电平,符合理论分析和实验设计的预期。

总结和反思:

这次实验由于准备不足以及连接线路的时候粗心大意,导致实验遇到种种困难。以后进行数字电路实验要根据实验器材提前做好实验准备,画出将要用的图表,方便实验的时候使用。