zynq7000 PL读写DDR3----实验笔记

环境:vivado2018.3

芯片: xc7z100ffg900-2

本实验参考资料主要来源:https://www.eefocus.com/antaur/blog/17-08/423773_0818c.html

实验目的:将ADC接收的数据先存入DDR3,待PS端读取完成后,再存入一批。

1、工程规划

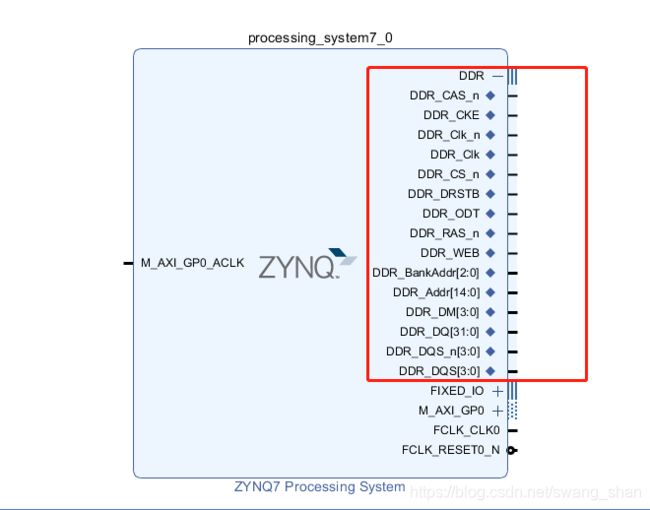

DDR芯片的管脚是绑定到Zynq的DDR接口上的。

而Zynq系统的这个DDR总线接口有是链接在其内部“Memory Interfaces”中的“DDR2/3,LPDDR2 Controller”可配置硬核上的。

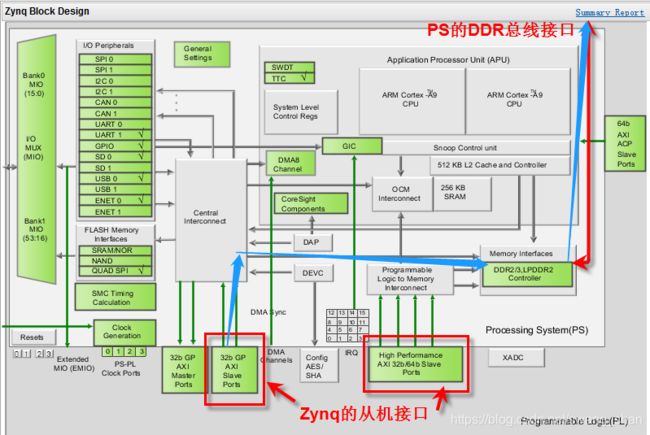

因此,要想PL访问板上的DDR3存储器,必须借道Zynq中的“Memory Interfaces----DDR2/3,LPDDR2 Controller”(后文简称“DDR3 Controller”)。在Zynq系统中,ARM Core(CPU)能够访问硬核“DDR3 Controller”,根据经验可以确定“DDR3 Controller”一定是一个从设备,而PL要想访问“DDR3 Controller”的话,PL一定要是一个主设备,由PL发起读写操作。

“DDR3 Controller”是封装在Zynq子系统中的,因此,PL必须连接Zynq的从机接口。本节使用普通的从机接口“32b GP AXI Slave Ports”。

交互数据将会经过Zynq子系统的内部总“Central Interconnect”转发给Memory Interfaces。具体数据交互路径如上图蓝色箭头。

根据上述分析,SoC系统集成方案框图如下:

2.Zynq系统裁剪

修改配置,裁剪掉在本项目中不需要的Zynq中的硬核。

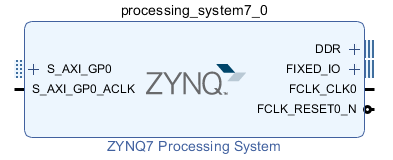

封装图如下:

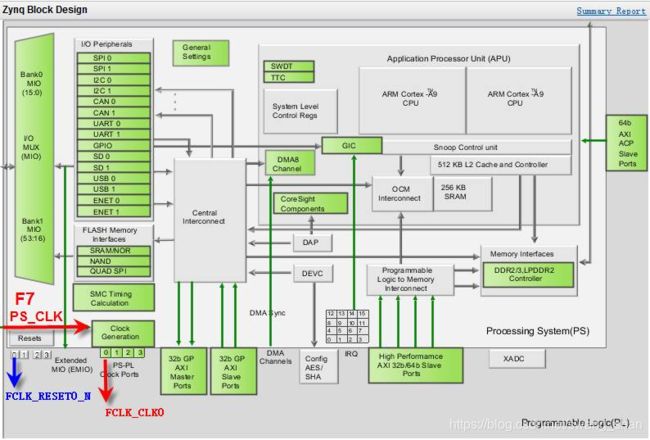

FCLK_CLK0和FCLK_RESET0_N是输出时钟和复位信号。这两个信号的出处已在上图中标注。这两个信号详情请见附录1.

利用FCLK_CLK0驱动PL端的时序逻辑。而将Y9管脚引入的100MHzGCLK信号旁路。

zynq子系统剪裁完毕。

3、生成AXI4-Lite Master IP

详细步骤见:https://www.eefocus.com/antaur/blog/17-08/423751_6cc0d.html

代码见:https://www.eefocus.com/antaur/blog/17-08/423773_0818c.html

4、完成Block Design

添加上一步生成的axi_master的IP核到block design,点击Run Connection Audomation后,如下图所示。彩色标注出的PL端的时钟信号和复位信号,均由Zynq子系统产生。GP接口速率低,更换使用HP接口。

按F6检查链接,检查无误后,点击Address Editor标签,可以看到相关的内存分配。内存映射相关见首页链接。

主机模块,使用的默认起始地址是0x4000_0000,这个在代码中定义的。也可在IP核的GUI中看到。从文档中知道,这个地址是向PL AXI Slave Port #0,即GP0的,Size是1G。

数据传输路径:(猜测)

PL 中的Master IP向0x4000_0000地址写入数据,经过PL中的AXI Interconnect直连,将会转发给GP0,GP0收到后,转给DDR.

硬件设计完毕。

5、Generate Bitstream

创建HDL Wrapper —> Run Synthesis(—> Schematic查看I/O Planning,根据需要进行管脚绑定)—> Generate Bitstream

如果BD有修改,则右键block design—> generate output products。系统会自动更新HDL wrapper。

不方便仿真,所以直接下板测试。

6、启用SDK

本实验启用了ARM,必须再SDK中进行SoC工程配置,否则zynq不会工作。

第一步:Vivado中File —>Export Hardware...(其中需要Include Bitstream)

第二步:Vivado中File —>Launch SDK

第三步:创建用户工程,File —>New —> Application Project

第四步:在helloword.c中编写相应代码,保存后,系统会自动编译。(因为系统默认设置Build Automatically,在Project栏中)

第六步:Program FPGA

SDK相关说明

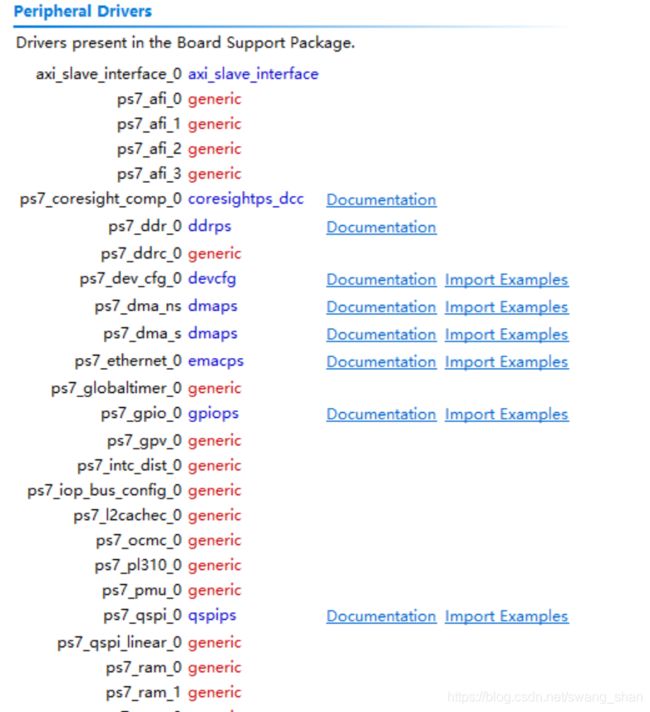

第一步export过来的文件夹下的system.hdf 和生成的板载支持库文件夹下的system.mss可以查看相关信息。