【Intel FPGA】D5005 使用笔记

项目总目标,在AFU中实现xx算法+DDR

1.FPGA device :1SX280HN2F43E2VG

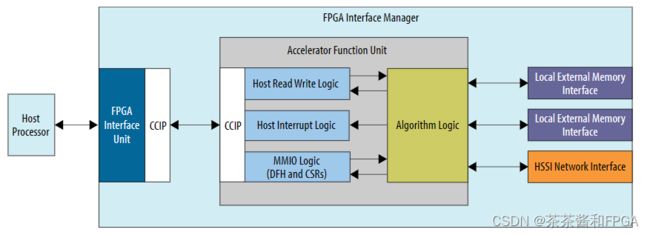

2 .硬件架构图

3.DDR信息

4.FIM (FPAG Interface Manager)

The FIM contains the FPGA logic to support the

accelerators, including the PCIe IP core, the Core Cache Interface protocol (CCI-P)

fabric, the on-board DDR memory interface and management engine.

afu(accelator functional unit)

function description:

1.The AFU is a function or set of functions that can be accelerated on an OPAE hardware platform

2.The AFU is described in RTL and the compiled with the OPAE SDK to generate an Accelerated Function(AF) image for the target hardware platform.

3.The AF image is used by OPAEto load the AFU to the PR region

main communication path between the host:

1.FPGA to host transactions

2.Host to FPGA(MMIO )tranactions:

AFU Design Componets

AFU high Level Block diagram

Typical AFU design

1) RTL description of the algorithm or function being accelerated

2) RTL description to implement the base requirements placed on AFUs by OPAE(eg DFH AFU ID in MMIO space )

3)Supportive infrastructure

a.Logic to map AFU CSRs into MMIO space

b,memory mastering logic

FPGA to host memory access

Local FPGA memory access

4)Debug and Performance Monitoring

a.Signal Tap with the Remote Debug feature

b.Performance monitoring and counters within the scope of the AFU

参考文档

1.ds1058 https://www.intel.com/content/www/us/en/docs/programmable/683568/current/introduction.html

2. OPAE Intel FPGA Linux Device Driver Architecture Guide https://www.intel.com/content/www/us/en/docs/programmable/683857/current/opae-linux-device-driver-architecture.html

3. D5005 https://www.intel.com/content/www/us/en/support/programmable/support-resources/devices/legacy-card-support.html