- Ligetron:基于MPC-In-The-Head范式的zkVM简介

1.引言前序博客有:Ligero和Ligetron中的MPC和ZKLigetron:NimNetwork开发的针对AI的zkVMLigeroInc.推出的Ligetron正在重新定义零知识技术的边界,利用最前沿的ZK系统将zkVM带到任何硬件设备上:可以直接从浏览器构建完整的zkApp,并将其部署到任何设备上——无需繁琐的编译过程,实现无缝的端到端功能。ZK无处不在,随处可用!Ligero的使命是

- Nexus zkVM 3.0 及未来:迈向模块化、分布式的零知识证明

mutourend

zkVMzkVM

1.引言2025年3月,Nexus团队发布了NexuszkVM3.0,本文将更详细地介绍其设计意图与功能。零知识虚拟机(zkVM)领域正在迅速演进,推动力来自于对可扩展、高效且可靠的系统的需求——这些系统应能够在不受计算规模、编程语言或底层架构限制的前提下,证明任意程序的正确执行。Nexus正是基于这一愿景推出了NexuszkVM3.0,它是一次经过深思熟虑的虚拟机重构,解决了长期存在的限制问题,

- 空间最小、速度最快:内存高效ZKP原理

mutourend

零知识证明零知识证明

1.引言在快速发展的区块链和密码学领域,经常听说,旨在扩展以太坊或解决大规模计算问题的速度超快的零知识虚拟机(zkVM,zero-knowledgeVirtualMachine)。然而,若要实现真正的隐私,ZKP应在本地运行。这一概念称为本地可验证计算,涉及实现极其节省空间的ZKP,用于本地且资源通常受限的设备——从嵌入式系统到物联网设备再到用户的网络浏览器。基本原则简单但至关重要:当与第三方共享

- SP1:基于Plonky3构建的zkVM

mutourend

zkVMzkVM

1.引言SP1为SuccictLab开源的,基于Plonky3构建的zkVM。开源代码见:https://github.com/succinctlabs/sp1(Rust)当前暂未实现onchain-verifier,但会采用标准的STARK->SNARKverifier。SP1zkVM基于的指令集为:riscv32im(与RISCZero的指令集一样)在SP1zkVM中运行某程序之前,需将该程序

- RISC Zero zkVM Host & Guest 101

mutourend

zkVMzkVM

1.引言在RISCZerozkVM应用程序中,host为运行RISCZerozkVM的机器(或系统)。host为不可信agent,负责设置zkVM环境和处理执行过程中的输入输出。host程序(代码),是指:zkVM应用中的host-native、不可信的部分。负责加载guest程序,并为guest程序提供必要的输入。若基于Bonsai构建,则无需编写host代码。zkVM应用中,host负责构建并

- ZK*FM:RISC Zero zkVM的形式化验证

mutourend

zkVMzkVM

1.引言开源代码见:https://github.com/risc0/risc0-lean4(Lean和Rust)ZK*FM为RISCZerozkVM的形式化验证:ZK:Thecomputerrantherightprogram。FM:Theprogramdidtherightthing。ZK*FM:Thecomputerdidtherightthing。可使用FM来证明RISCZero的ZKto

- RISC Zero zkVM guest程序优化技巧 及其 与物理CPU的关键差异

mutourend

zkVMzkVM

1.引言RISCZerozkVM设计并实现为与物理CPU功能类似。从而对于RISCZerozkVMguest程序:可使用通用编程语言(如Rust)和通用工具(如Cargo,LLVM)。通常,也可使用通用优化技术来优化。在RISCZerozkVM的某应用中,guest程序为zkVM待执行和证明的代码。guest应具有reading、writting和committing的基本功能,具体为:1)读取输

- 技术探秘:在RISC Zero中验证FHE——由隐藏到证明:FHE验证的ZK路径(1)

mutourend

零知识证明零知识证明

1.引言开源代码实现见:https://github.com/hashcloak/fhe_risc0_zkvm(Rust)https://github.com/weikengchen/vfhe-profiled(Rust)https://github.com/l2iterative/vfhe0(Rust)L2IVResearch团队近期尝试用ZKP来验证FHE,原因在于如下2大应用场景的出现:1)

- Reed-Solomon Codes及其与RISC Zero zkVM的关系

mutourend

zkVMzkVM

1.引言前序博客:Reed-SolomonCodes——RS纠错码Reed-SolomonCodes当前广泛用于:QRcodes二维码Cellularcommunication蜂窝通信STARKs2.简化的Reed-SolomonEncoding(RS编码)所谓encoding(编码),是指:将messages转换为codewords的系统。即:Enc:{messages}→{codewords}

- RISC Zero zkVM架构

mutourend

zkVMzkVM

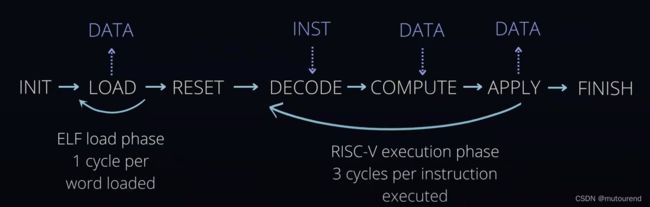

1.引言RISCZerozkVM为:基于FRI+PLONK构建的采用VonNeumann架构的ZKMachine将RISC-V微控制器具化为某基于STARK的证明系统,的微架构和编码机制。2.Row(Time)Structure一个cycle对应1个memorytransaction,对用户传入的程序elf可执行文件的处理流程为:1)INIT:初始化阶段。有特殊的初始化cycle,用于重置状态。2

- Continuations:扩展RISC Zero zkVM支持(无限)大计算

mutourend

zkVMzkVM

1.引言前序博客:Risc0:使用Continunations来证明任意EVM交易RISCZero在2013年5月的0.15版本中,引入了Continuous机制:移除了证明生成时的“cyclelimit”限制解锁了在RISCZerozkVM中运行EVMinterpreter或WASMinterpreter的能力扩展为可支持(无限)大计算Continuous机制的核心思想为:将execution切

- RISC Zero zkVM 白皮书

mutourend

zkVMzkVM

1.引言RISCZero提供了开源的虚拟机+零知识证明系统,即zero-knowledgevirtualmachine(简称zkVM)。当在zkVM中执行某RISC-V二进制文件时,其输出为:二进制文件执行结果+一个computationalreceipt,提供了计算完整性的零知识证明。RISCZero的证明系统采用zk-STARK,基于以下关键要素:FRI协议DEEP-ALI基于HMAC-SHA

- Risc zero ZKVM:zk-STARKs + RISC-V

mutourend

零知识证明zkVMrisc-v

1.引言Risczero定位为:TheGeneralPurposeZero-KnowledgeVM.ProveanyComputation.VerifyInstantly.开源代码见:https://github.com/risc0/risc0TheRISCZeroZKVMisaverifiablecomputerthatworkslikearealembeddedRISC-Vmicroproce

- RISC0:Towards a Unified Compilation Framework for Zero Knowledge

mutourend

zkVM零知识证明

1.引言本文主要摘自RISC0(RISCZERO)创始人BrianRetford在CompilerandComposabilityinZKP上的演讲内容。2.何为ZKVM?3.密集型计算加速策略4.MLIR参考资料[1]CompilerandComposabilityinZKP

- RISC-V与RISC Zero zkVM的关系

mutourend

zkVMzkVM

1.引言本文基本结构为:编程语言背景介绍RISC-V虚拟机作为zkVM电路为何选择RISC-V?2.编程语言背景介绍高级编程语言不专门针对某个架构,其便于人类编写。高级编程语言代码,经编译器编译后,会生成针对专门某架构的汇编代码,汇编代码是供机器使用的。也可以直接编写汇编代码:以上汇编代码示例中:蓝色框表示:所编码的数据和指令。黄色框:为对蓝色框的反汇编。黑色框:为这些opcodes的位置信息。可

- 针对zkVM中Memory Consistency Checks的Polynomial IOPs

mutourend

zkVMzkVM

1.引言主要参考YuncongZhang等人2023年论文《PolynomialIOPsforMemoryConsistencyChecksinZero-KnowledgeVirtualMachines》。在设计zkvm时,需检查其所有组件的功能一致性,包括:instructionfetcher寄存器文件算术化逻辑单元内存其中最具挑战的技术协议为Memoryconsistencycheck(MCC

- RISC Zero zkVM性能指标

mutourend

zkVMzkVM

1.引言对应代码:https://github.com/risc0/risc0(C++和Rust)运行如下指令,进行性能评估:cargorun-r--exampleloop//CPUcargorun-r-Fmetal--exampleloop//MetalGPUcargorun-r-Fcuda--exampleloop//CUDAGPUcargobench--benchfib//默认为CPU,可配

- zkVM设计性能分析

mutourend

zkVMzkVM

1.引言本文主要参考:2023年9月ZKSummit10WeiDai@1k(x)&TerryChung@1k(x)分享视频ZK10:AnalysisofzkVMDesigns-WeiDai&TerryChung当前有各种zkVM,其设计思想各有不同,且各有取舍,本文重点对现有各zkVM设计进行分析。zkVMs寒武纪大爆发:2020年之前的zkVM方案均是学术性的,不具备实用性,具体有:TinyRA

- Polygon Miden:扩展以太坊功能集的ZK-optimized rollup

mutourend

zkVMzkVM

1.引言PolygonMiden定位为zkVM,定于2023年Q4上公开测试网。zk、zkVM、zkEVM及其未来中指出,当前主要有3种类型的zkVM,括号内为其相应的指令集:mainstream(WASM,RISC-V)EVM(EVMbytecode)ZK-Optimized(专为零知识证明优化的新型指令集,如Cairo的指令集和zkSync的指令集)PolygonMiden为:ZK-optim

- zk、zkVM、zkEVM及其未来

mutourend

zkVM区块链

1.引言zk(zero-knowledge)proof:可保证计算的完整性、正确性和隐私性,在区块链扩容和隐私领域大有可为。zk-SNARK和zk-STARK各具优势,二者结合潜力无穷。zkVM可为应用增加零知识证明,zkVM可以按mainstrem、EVM或新构建的指令集进行分类。EVM兼容性包括EVM兼容性、等价性和规范级兼容性。zkEVM是一个EVM兼容且零知识证明友好的环境。它可以分为基于

- 基于Nova/SuperNova的zkVM

mutourend

zkVMzkVM

1.引言本文为2023年3月13~4月7日ZKSpringResidencyinVietnam上,由PSE团队、OrochiNetwork团队、0xPARC团队、Oskar(独立个人)以及Delv团队联合发布。Nova:借助IncrementalVerifiableComputation(IVC)和foldingscheme,Nova可更高效地执行重复相同的代码块。Nova采用的安全假设为GLOG

- Research Day 2023:Succinct ZKP最新进展

mutourend

零知识证明零知识证明

1.引言主要见YingTong在ResearchDay2023上视频分享:AdvancesintheEfficiencyofSuccinctProofs-YingTongZKP技术可用于:1)Verifiablevirtualmachine:如各种zkEVM和zkVM。2)verifiablecloudcomputing:2015年论文《ClusterComputinginZeroKnowledg

- zkLLVM:nil Foundation开发的电路编译器

mutourend

零知识证明零知识证明

1.引言zkLLVM:nilFoundation开发的电路编译器,不是zkVM。不过,“zkLLVM+proofmarket”可构建zkVM。开源代码见:zkLLVMCircuitCompiler(C++)zkLLVM可:将高级编程语言编写的电路编译为LLVMIR(IntermediateRepresentation)bytecode表示;当前支持C/C++(Clang15),即将支持Rust语言

- 智能合约开发——Sui/Move vs. Solana/Rust

mutourend

智能合约智能合约

1.引言前序博客有:zkMove——针对Move合约生态的zkVM定位为高性能L1的Aptos和Sui,均采用Move合约编程语言。Solana也定位为高性能L1,但其采用Rust合约编程语言。本文重点对比Sui/Move和Solana/Rust合约编程语言。【Aptos/Move为不同的Move变种,有细微的差别。不过只要原生支持Movebytecode,则所有主要Move优势适于所有Move变

- zkMove——针对Move合约生态的zkVM

mutourend

zkVM零知识证明

1.引言Move为不同于Solidity的,开源的安全的智能合约开发语言,最早由Facebook为Diem链创造开发。不过,Move本身设计为与平台无关的语言,具有通用的库、工具,并使得采用完全不同数据模型和执行模型的链的开发者社区都可使用Move。当前支持Move合约的链有:Sui:定位为具有高吞吐量、低延迟、面向资产编程模式的下一代智能合约平台,采用Move语言进行合约开发。当前处于devne

- BulletproofVM:Avalanche上的zkVM

mutourend

zkVM零知识证明

1.引言开源代码见:https://github.com/usmaneth/BulletproofVM(Rust)BulletproofVM为Avalanche上的基于Bulletproofs证明系统构建的zkVM,其主要特性为:MaintainsastateconsistingofaccountswithbalancesandassetsExecutesstandardtransactionsf

- 多线程编程之join()方法

周凡杨

javaJOIN多线程编程线程

现实生活中,有些工作是需要团队中成员依次完成的,这就涉及到了一个顺序问题。现在有T1、T2、T3三个工人,如何保证T2在T1执行完后执行,T3在T2执行完后执行?问题分析:首先问题中有三个实体,T1、T2、T3, 因为是多线程编程,所以都要设计成线程类。关键是怎么保证线程能依次执行完呢?

Java实现过程如下:

public class T1 implements Runnabl

- java中switch的使用

bingyingao

javaenumbreakcontinue

java中的switch仅支持case条件仅支持int、enum两种类型。

用enum的时候,不能直接写下列形式。

switch (timeType) {

case ProdtransTimeTypeEnum.DAILY:

break;

default:

br

- hive having count 不能去重

daizj

hive去重having count计数

hive在使用having count()是,不支持去重计数

hive (default)> select imei from t_test_phonenum where ds=20150701 group by imei having count(distinct phone_num)>1 limit 10;

FAILED: SemanticExcep

- WebSphere对JSP的缓存

周凡杨

WAS JSP 缓存

对于线网上的工程,更新JSP到WebSphere后,有时会出现修改的jsp没有起作用,特别是改变了某jsp的样式后,在页面中没看到效果,这主要就是由于websphere中缓存的缘故,这就要清除WebSphere中jsp缓存。要清除WebSphere中JSP的缓存,就要找到WAS安装后的根目录。

现服务

- 设计模式总结

朱辉辉33

java设计模式

1.工厂模式

1.1 工厂方法模式 (由一个工厂类管理构造方法)

1.1.1普通工厂模式(一个工厂类中只有一个方法)

1.1.2多工厂模式(一个工厂类中有多个方法)

1.1.3静态工厂模式(将工厂类中的方法变成静态方法)

&n

- 实例:供应商管理报表需求调研报告

老A不折腾

finereport报表系统报表软件信息化选型

引言

随着企业集团的生产规模扩张,为支撑全球供应链管理,对于供应商的管理和采购过程的监控已经不局限于简单的交付以及价格的管理,目前采购及供应商管理各个环节的操作分别在不同的系统下进行,而各个数据源都独立存在,无法提供统一的数据支持;因此,为了实现对于数据分析以提供采购决策,建立报表体系成为必须。 业务目标

1、通过报表为采购决策提供数据分析与支撑

2、对供应商进行综合评估以及管理,合理管理和

- mysql

林鹤霄

转载源:http://blog.sina.com.cn/s/blog_4f925fc30100rx5l.html

mysql -uroot -p

ERROR 1045 (28000): Access denied for user 'root'@'localhost' (using password: YES)

[root@centos var]# service mysql

- Linux下多线程堆栈查看工具(pstree、ps、pstack)

aigo

linux

原文:http://blog.csdn.net/yfkiss/article/details/6729364

1. pstree

pstree以树结构显示进程$ pstree -p work | grep adsshd(22669)---bash(22670)---ad_preprocess(4551)-+-{ad_preprocess}(4552) &n

- html input与textarea 值改变事件

alxw4616

JavaScript

// 文本输入框(input) 文本域(textarea)值改变事件

// onpropertychange(IE) oninput(w3c)

$('input,textarea').on('propertychange input', function(event) {

console.log($(this).val())

});

- String类的基本用法

百合不是茶

String

字符串的用法;

// 根据字节数组创建字符串

byte[] by = { 'a', 'b', 'c', 'd' };

String newByteString = new String(by);

1,length() 获取字符串的长度

&nbs

- JDK1.5 Semaphore实例

bijian1013

javathreadjava多线程Semaphore

Semaphore类

一个计数信号量。从概念上讲,信号量维护了一个许可集合。如有必要,在许可可用前会阻塞每一个 acquire(),然后再获取该许可。每个 release() 添加一个许可,从而可能释放一个正在阻塞的获取者。但是,不使用实际的许可对象,Semaphore 只对可用许可的号码进行计数,并采取相应的行动。

S

- 使用GZip来压缩传输量

bijian1013

javaGZip

启动GZip压缩要用到一个开源的Filter:PJL Compressing Filter。这个Filter自1.5.0开始该工程开始构建于JDK5.0,因此在JDK1.4环境下只能使用1.4.6。

PJL Compressi

- 【Java范型三】Java范型详解之范型类型通配符

bit1129

java

定义如下一个简单的范型类,

package com.tom.lang.generics;

public class Generics<T> {

private T value;

public Generics(T value) {

this.value = value;

}

}

- 【Hadoop十二】HDFS常用命令

bit1129

hadoop

1. 修改日志文件查看器

hdfs oev -i edits_0000000000000000081-0000000000000000089 -o edits.xml

cat edits.xml

修改日志文件转储为xml格式的edits.xml文件,其中每条RECORD就是一个操作事务日志

2. fsimage查看HDFS中的块信息等

&nb

- 怎样区别nginx中rewrite时break和last

ronin47

在使用nginx配置rewrite中经常会遇到有的地方用last并不能工作,换成break就可以,其中的原理是对于根目录的理解有所区别,按我的测试结果大致是这样的。

location /

{

proxy_pass http://test;

- java-21.中兴面试题 输入两个整数 n 和 m ,从数列 1 , 2 , 3.......n 中随意取几个数 , 使其和等于 m

bylijinnan

java

import java.util.ArrayList;

import java.util.List;

import java.util.Stack;

public class CombinationToSum {

/*

第21 题

2010 年中兴面试题

编程求解:

输入两个整数 n 和 m ,从数列 1 , 2 , 3.......n 中随意取几个数 ,

使其和等

- eclipse svn 帐号密码修改问题

开窍的石头

eclipseSVNsvn帐号密码修改

问题描述:

Eclipse的SVN插件Subclipse做得很好,在svn操作方面提供了很强大丰富的功能。但到目前为止,该插件对svn用户的概念极为淡薄,不但不能方便地切换用户,而且一旦用户的帐号、密码保存之后,就无法再变更了。

解决思路:

删除subclipse记录的帐号、密码信息,重新输入

- [电子商务]传统商务活动与互联网的结合

comsci

电子商务

某一个传统名牌产品,过去销售的地点就在某些特定的地区和阶层,现在进入互联网之后,用户的数量群突然扩大了无数倍,但是,这种产品潜在的劣势也被放大了无数倍,这种销售利润与经营风险同步放大的效应,在最近几年将会频繁出现。。。。

如何避免销售量和利润率增加的

- java 解析 properties-使用 Properties-可以指定配置文件路径

cuityang

javaproperties

#mq

xdr.mq.url=tcp://192.168.100.15:61618;

import java.io.IOException;

import java.util.Properties;

public class Test {

String conf = "log4j.properties";

private static final

- Java核心问题集锦

darrenzhu

java基础核心难点

注意,这里的参考文章基本来自Effective Java和jdk源码

1)ConcurrentModificationException

当你用for each遍历一个list时,如果你在循环主体代码中修改list中的元素,将会得到这个Exception,解决的办法是:

1)用listIterator, 它支持在遍历的过程中修改元素,

2)不用listIterator, new一个

- 1分钟学会Markdown语法

dcj3sjt126com

markdown

markdown 简明语法 基本符号

*,-,+ 3个符号效果都一样,这3个符号被称为 Markdown符号

空白行表示另起一个段落

`是表示inline代码,tab是用来标记 代码段,分别对应html的code,pre标签

换行

单一段落( <p>) 用一个空白行

连续两个空格 会变成一个 <br>

连续3个符号,然后是空行

- Gson使用二(GsonBuilder)

eksliang

jsongsonGsonBuilder

转载请出自出处:http://eksliang.iteye.com/blog/2175473 一.概述

GsonBuilder用来定制java跟json之间的转换格式

二.基本使用

实体测试类:

温馨提示:默认情况下@Expose注解是不起作用的,除非你用GsonBuilder创建Gson的时候调用了GsonBuilder.excludeField

- 报ClassNotFoundException: Didn't find class "...Activity" on path: DexPathList

gundumw100

android

有一个工程,本来运行是正常的,我想把它移植到另一台PC上,结果报:

java.lang.RuntimeException: Unable to instantiate activity ComponentInfo{com.mobovip.bgr/com.mobovip.bgr.MainActivity}: java.lang.ClassNotFoundException: Didn't f

- JavaWeb之JSP指令

ihuning

javaweb

要点

JSP指令简介

page指令

include指令

JSP指令简介

JSP指令(directive)是为JSP引擎而设计的,它们并不直接产生任何可见输出,而只是告诉引擎如何处理JSP页面中的其余部分。

JSP指令的基本语法格式:

<%@ 指令 属性名="

- mac上编译FFmpeg跑ios

啸笑天

ffmpeg

1、下载文件:https://github.com/libav/gas-preprocessor, 复制gas-preprocessor.pl到/usr/local/bin/下, 修改文件权限:chmod 777 /usr/local/bin/gas-preprocessor.pl

2、安装yasm-1.2.0

curl http://www.tortall.net/projects/yasm

- sql mysql oracle中字符串连接

macroli

oraclesqlmysqlSQL Server

有的时候,我们有需要将由不同栏位获得的资料串连在一起。每一种资料库都有提供方法来达到这个目的:

MySQL: CONCAT()

Oracle: CONCAT(), ||

SQL Server: +

CONCAT() 的语法如下:

Mysql 中 CONCAT(字串1, 字串2, 字串3, ...): 将字串1、字串2、字串3,等字串连在一起。

请注意,Oracle的CON

- Git fatal: unab SSL certificate problem: unable to get local issuer ce rtificate

qiaolevip

学习永无止境每天进步一点点git纵观千象

// 报错如下:

$ git pull origin master

fatal: unable to access 'https://git.xxx.com/': SSL certificate problem: unable to get local issuer ce

rtificate

// 原因:

由于git最新版默认使用ssl安全验证,但是我们是使用的git未设

- windows命令行设置wifi

surfingll

windowswifi笔记本wifi

还没有讨厌无线wifi的无尽广告么,还在耐心等待它慢慢启动么

教你命令行设置 笔记本电脑wifi:

1、开启wifi命令

netsh wlan set hostednetwork mode=allow ssid=surf8 key=bb123456

netsh wlan start hostednetwork

pause

其中pause是等待输入,可以去掉

2、

- Linux(Ubuntu)下安装sysv-rc-conf

wmlJava

linuxubuntusysv-rc-conf

安装:sudo apt-get install sysv-rc-conf 使用:sudo sysv-rc-conf

操作界面十分简洁,你可以用鼠标点击,也可以用键盘方向键定位,用空格键选择,用Ctrl+N翻下一页,用Ctrl+P翻上一页,用Q退出。

背景知识

sysv-rc-conf是一个强大的服务管理程序,群众的意见是sysv-rc-conf比chkconf

- svn切换环境,重发布应用多了javaee标签前缀

zengshaotao

javaee

更换了开发环境,从杭州,改变到了上海。svn的地址肯定要切换的,切换之前需要将原svn自带的.svn文件信息删除,可手动删除,也可通过废弃原来的svn位置提示删除.svn时删除。

然后就是按照最新的svn地址和规范建立相关的目录信息,再将原来的纯代码信息上传到新的环境。然后再重新检出,这样每次修改后就可以看到哪些文件被修改过,这对于增量发布的规范特别有用。

检出