基于ARM和FPGA的数字示波器设计——QMJ

文章目录

- 前言

- 一、便携式数字示波器设计

-

- 1.1 设计原理及思路

- 1.2 系统技术指标

- 二、示波器各模块作用

-

- 2.1 LCT2308介绍

- 2.2 adc.v模块介绍

- 2.3 time_scaler.v模块介绍

- 2.4 trigger.v模块介绍

- 2.5 vga.v模块介绍

- 三、VGA两种像素数据传递方式

- 四、硬件介绍及结果分析

- 五、工具使用

-

- 5.1 运用逻辑分析仪及Modelism

- 5.2 制作嵌入式linux-SD系统启动卡

- 5.3 学习HPS和FPGA的地址映射

- 5.4 将电脑与开发板通过NFS进行挂载

- 六、设计过程中方向上出现的问题

前言

本设计是一个4通道便携式数字示波器,采用DE1-SOC双核心开发板进行设计。示波器的数模转换器采用LCT2308芯片实现。整个系统的设计由两部分完成,一是完成FPGA硬件电路的设计;二是使用ARM设计系统的软件功能。

本便携式数字示波器具有体积小、重量轻及低功耗的优点。使用的工具包括:Quertus II 18.0,Modelism,逻辑分析仪,嵌入式linux -SD系统启动卡。

目前实现的功能,可以调整波形信号在显示器中进行上下平移,时间轴缩放及纵轴缩放。

一、便携式数字示波器设计

1.1 设计原理及思路

示波器设计如图1-1所示,DE1-SOC开发板通过板载LCT2308芯片采集模拟信号。使用ARM通过轻量级HPS-to-FPGA桥连接的IP核PIO,控制FPGA模块,此IP核PIO被定义为CFG端口。CFG端口会连续传输32bit数据,其中8bit用于识别FPGA模块,其余24bit属于FPGA模块的控制参数。

adc.v模块通过SPI总线与LCT2308芯片连接,并从LCT2308芯片被设置的采样通道中获取波形数据。

然后将这些波形数据送入到time_scaler.v模块,该模块以N个波形数据舍弃N-1个的方式实现所需的有效采样率。

波形数据传递到触发模块,这些波形数据也被传递到触发器模块,该触发模块将等待外界和来自触发器模块的触发信号。当两个触发信号发生时,触发模块开始存储接下来的640个数据点,并将波形数据写入到片上存储器SRAM。

vga.v读取片上存储器中的波形数据,将波形数据转换成像素数据发送至VGA。

1.2 系统技术指标

波形电压:0V~4.096V

测量频率范围:0~500KHz

存储深度:640

采样通道:4通道

显示模式:640*480@60Hz

VGA时钟频率:25MHz

FPGA时钟频率:50MHz

二、示波器各模块作用

2.1 LCT2308介绍

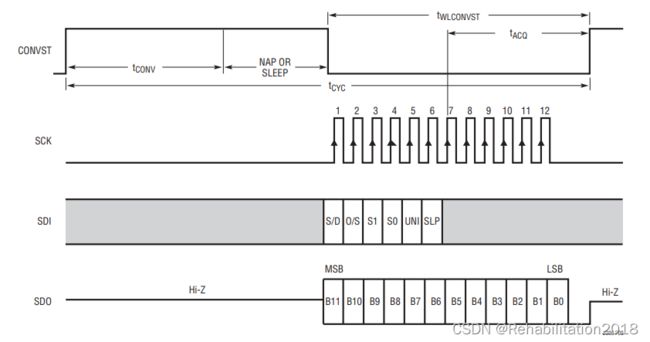

DE1-SOC开发板板载LCT2308(ADC)结构如图2-1所示,是一款12bit高精度逐次逼近型模数转换芯片,拥有 8 个模拟输入通道,具有高达 500 kSPS 的采 样速率以及一个兼容串行外设接口(SPI) 。

SPI总线包括4条逻辑线,定义如下:

CONVST:片选信号,由主机发送,以控制与从机的通信,低电平为有效信号;

SCK:串行时钟信号,由主机产生发送给从机;

SDI:主机输出,从机输入(数据来自主机),选择LCT2308的采样通道;

SDO:主机输入,从机输出(数据来自从机),传输采样数据。

注:产生时钟的一侧称为主机,另一侧称为从机。

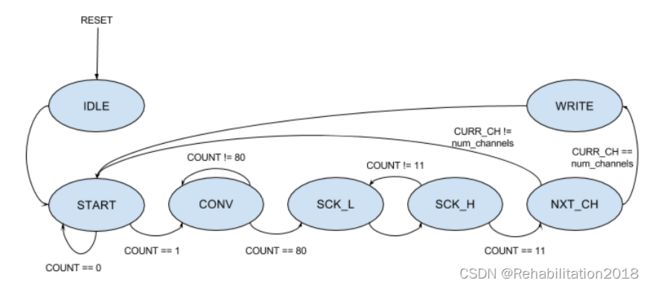

2.2 adc.v模块介绍

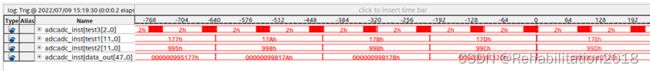

LCT2308对波形采样一个点,经量化编码为12bit数据,通过SPI总线传输给adc.v模块。adc.v模块将通过图2-3的FSM流程持续接收4个通道的波形数据,并整合为48bit。FSM处在WRITE状态会设置一个有效标志位data_val,将数据传输信号反馈给time_scaler.v模块。

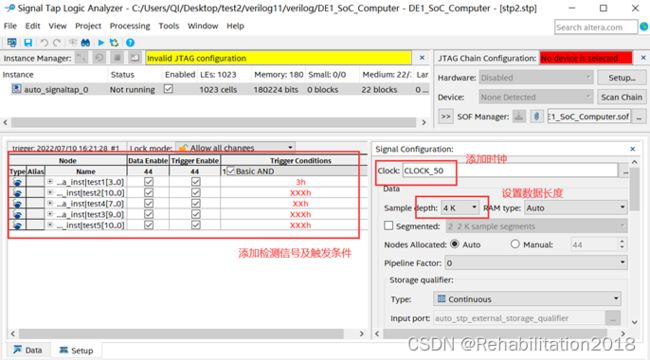

在FPGA开发板运行过程中,可通过逻辑分析仪检测FPGA模块中数据的变化。图2-4中test3端口表示adc.v模块状态机的变化;test1端口表示采样通道1的数据;test2端口表示采样通道2的数据;data_out端口从采样通道得到的数据整合成48bit。

2.3 time_scaler.v模块介绍

该模块从adc.v模块中接收到的每N+1个样本中删除N个样本,实现显示器波形横向的缩放,N值可通过CFG配置寄存器进行配置。具体实现则是通过创建一个计数器来完成的,该计数器在adc.v模块每次传递样本时递增,并在达到N值时重置为0。样本仅在计数器为0时传递到下一阶段。

图2-5中,使用test1端口检测计数器变化;out_msg端口接收来自adc.v模块的48bit波形数据。当计数器为0时,将对应的波形数据传递到下一个trigger.v模块。

2.4 trigger.v模块介绍

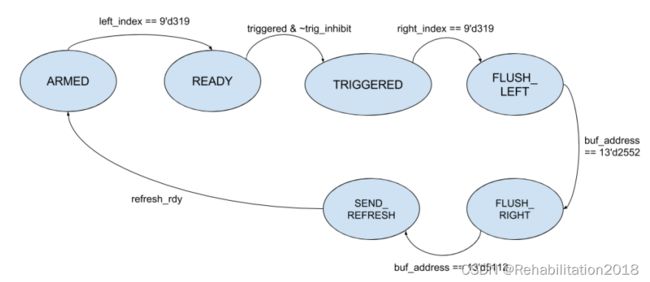

在ARMED状态下,缓冲区left_buffer需要保存320个数据点。当缓冲区保存到320个数据点,FSM会进入READY状态,等待两个触发信号,在等待触发条件时,缓冲区left_buffer持续更新数据点。当满足触发条件时,另有320个数据点在TRIGGERED状态被送入缓冲区right_buffer。

当缓冲区right_buffer保存320个数据点,将在FLUSH_LEFT状态和FLUSH_RIGHT状态把缓冲区left_buffer和right_buffer的数据点写入到片上存储器SRAM。FSM进入SEND_REFREESH状态,会向vga.v模块指示有新数据。

trigger.v模块在READY状态等待接收两个触发条件,分别来自triggerer.v模块和外界信号。其中外界信号由按键触发,triggerer.v模块能够进行边沿和脉冲触发,支持的五种模式是上升沿、下降沿、脉冲大于、脉冲小于和脉冲等于。

图2-7中test1检测该模块的状态机;test2检测两种触发信号同时存在的情况;test3和test4检测状态机在FLUSH_LEFT和FLUSH_RIGHT状态下,片上存储器存储通道1和通道2的640个波形数据点。

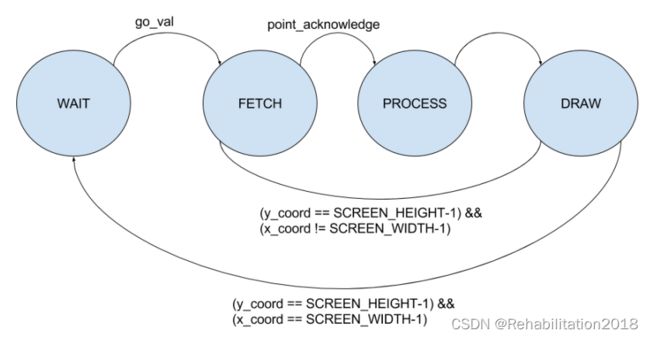

2.5 vga.v模块介绍

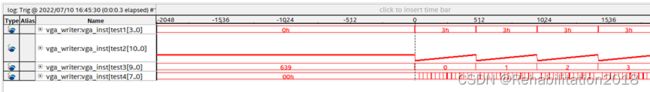

vga.v模块接收来自trigger.v模块的“go_val”的信号,开始从片上存储器提取数据。FSM的FETCH状态将接收48bit数据分离成4个12bit,并分别进行按比例放大。PRCOESS和DRAM状态将波形数据转换成rgb,实现的方式,准备两个置零的计数器,计数器A从0计数到479,计数器B加1,直到计数器B等于639。

这个过程计数器B每变化一次,向计数器A送入一个由12bit转换成11bit波形数据,将波形数据与计数器A数值比较,相等情况rgb为通道波形的rgb,否则rgb为0,即黑色。

图2-9中test1表示vga.v模块的状态机变化;test2检测计数器A;test3检测计数器B;test4表示得到rgb数据。

三、VGA两种像素数据传递方式

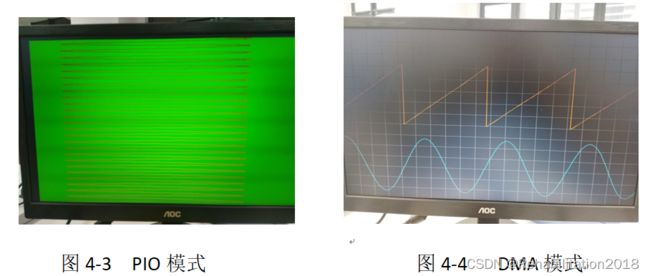

对于本设计中,vga.v模块的rgb数据传递到显示器的过程,分别应用PIO模式和DMA模式来实现。

DMA模式下,CPU并不全程参与数据的传送工作,只需下达命令即可。DMA方式下有控制器和通道,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈给CPU,这样就很大程度上减轻了CPU资源占有率。

PIO模式下通过CPU来控制硬盘和内存之间的数据传输,是一种通过CPU执行I/O端口指令来进行数据的读写的数据交换模式。

DMA模式与PIO模式的区别就在于,DMA模式不过分依赖CPU,可以大大节省系统资源,二者在传输速度上的差异并不十分明显。

四、硬件介绍及结果分析

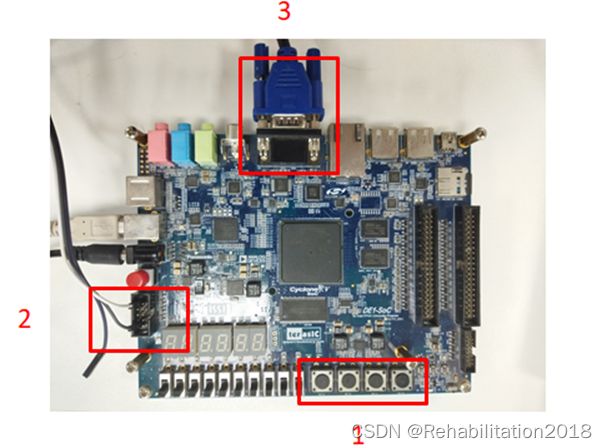

由STM32开发板产生正弦波和锯齿波两种模拟信号,信号频率为15hz,引脚使用如图4-1所示。

DE1-SOC开发板工作频率是50Mhz,图4-2中方框1表示按键,用于对 FPGA模块初始化;方框2表示LTC2308连接信号源;方框3表示VGA连接显示器。

图4-3的实验结果是在设置开发板的时钟频率是10KHz,VGA的时钟频率是25MHz的情况下得到的。这种时钟频率分配的状况下,显示器呈左右扫描的方式显示波形。并且在观察实验现象时,显示器会间断显示波形的情况。

原因分析,VGA的25MHz时钟频率下获取开发板10KHz处理得到的数据,这种条件下,VGA显示一组像素数据之后,需要等待开发板对下一组波形数据的处理。若是将开发板的时钟频率调到25MHz或者50MHz,则VGA不能准确的接收到像素数据,将在显示器上呈现黑屏现象。

然而,通过调用VGA_controller和DMA 等IP核,将被用来解决上面遇到的问题,其实验结果如图4-4所示。DMA(Direct Memory Access,直接内存存取),它允许不同速度的硬件装置来沟通,而不需要CPU的大量中断负载。

PIO模式下硬盘和内存之间的数据传输是由CPU来控制的;而在DMA模式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送。并且在DMA模式下,存在SRAM与FIFO等IP核,起到DMA和外设或存储器之间的缓冲器的作用。

IP核VGA_contronller可以设置的显示器扫描方式为上下扫描。

五、工具使用

5.1 运用逻辑分析仪及Modelism

使用Modelism对FPGA模块进行仿真,以理解FPGA模块的状态机。

图5-1的测试文件中,通过读取自己设计的波形数据以及CFG的配置信息,并依靠多个测试端口(test1、test2、test3)来检测FPGA模块中状态机和关键参数的变化,以此充分的理解verilog程序的设计框架。

运用逻辑分析仪对FPGA模块在开发板运行过程中检测状态机及端口变化,便于筛查出波形数据出错的位置。

详细的步骤讲解可参考下面链接对应的视频。

https://www.bilibili.com/video/BV1o54y1L7ut?vd_source=bf69d71b17066eefdcd36c6207919226

5.2 制作嵌入式linux-SD系统启动卡

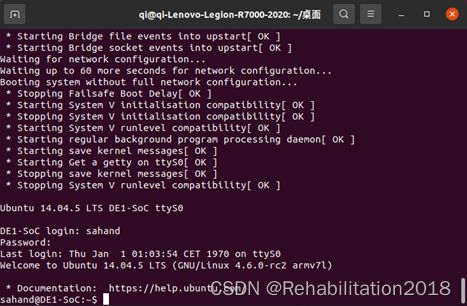

实现示波器软件功能,需要linux系统通过linux-SD系统启动卡控制开发板ARM芯片,达到FPGA和ARM的联合应用。

对于linux-SD系统启动卡的制作,需要在SD卡的a2、ext3和fat3分区,准备以下的文件,制作的流程请参考SoC-FPGA Design Guide DE1-SoC Edition.pdf的第13章节以及第11.1章节。

sdcard/

├── a2

│ └── preloader-mkpimage.bin

├── ext3_rootfs.tar.gz

└── fat32

├── socfpga.dtb

├── socfpga.rbf

├── u-boot.img

├── u-boot.scr

└── zImage

通过linux系统的minicom终端控制DE1-SOC设备,如图5-3所示。

5.3 学习HPS和FPGA的地址映射

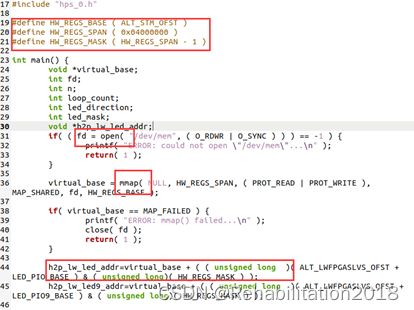

将开发板中存储器的物理地址映射为应用程序软件可以访问的虚拟地址,需要进行以下操作。

首先,open 通过系统调用打开内存设备驱动程序" /dev/mem "。

然后mmap通过系统调用用于将HPS物理地址映射为由void指针变量virtual_base表示的虚拟地址。代码将外围区域的物理基地址(HW_REGS_BASE = 0xfc000000)映射为一个基于虚拟地址的virtual_base。对于任何外围区域的控制器,用户可以通过其相对于外围区域的偏移量与基于的虚拟地址virtual_base进行叠加来计算任何外围区域的控制器的虚拟地址。

详细的操作步骤可参考下面链接对应的文档。

https://blog.csdn.net/liluxiang333/article/details/113626965

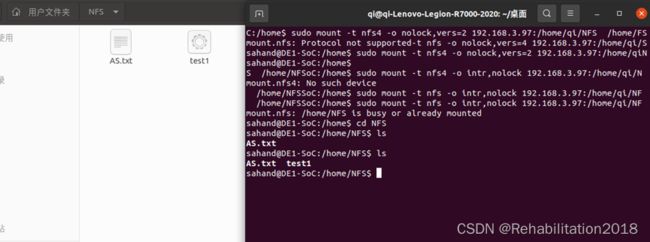

5.4 将电脑与开发板通过NFS进行挂载

通过网线连接电脑和开发板,便于将软件代码得到的可执行文件放入到SD卡中执行。

操作步骤:

第一步

https://blog.csdn.net/thisway_diy/article/details/111474111

第二步

确保开发板可以 ping 通 Ubuntu

minicom终端 使用ifconfig命令

自动出现:inet addr:10.42.0.98 (开发板的IP)

在终端使用 hostname -I

出现两个IP 分别是ubuntu 开发板的

使用ping 确保开发板和ubuntu能传输信号

第三步

在minicom终端挂载

https://blog.csdn.net/LMmcu_2012/article/details/78566067

第五步 取消挂载

退出minicom终端

六、设计过程中方向上出现的问题

(1)面对ARM和FPGA联合应用,首先应该找一个例程,运用例程来快速的理解地址映射的问题;

(2)忽略逻辑分析仪工具的使用范畴;

(3)过于纠结示波器文字信息编译问题。