Verilog作业(二)

〇、关于本文

本文我的Verilog课程作业,由于我尚处在初学阶段,并且这门课和我实际工作的关系并不大,因此代码仅供参考。

我使用的编译环境为iverilog,在Windows下运行。

一、将一个波形的频率增大4倍

设计一个周期为10ns的时钟clk1,占空比为50%,并设计一个四分频模块,将clk1分为周期为2.5ns的时钟clk2

文件a.v代码

module clk_mul_4(clk_out, clr, clk1); input clk1; //输入时钟 input clr; //复位端 output clk_out; //输出分频时钟 reg clk_out; integer counter = 0; always @(negedge clr or posedge clk1) begin if(!clr) begin clk_out = 0; counter = 0; end else begin counter = counter + 1; if(counter == 3) begin clk_out = ~clk_out; counter = 1; end end end endmodule

文件b.v代码

module test();

reg clk1;

reg clr;

wire clk_out;

clk_mul_4 dut(.clk_out(clk_out), .clr(clr), .clk1(clk1));

initial

begin

clk1 = 0; clr = 0;

#5 clr = 1;

end

always #5 clk1 = ~clk1;

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1,test);

$dumpon();

#1000

$dumpoff();

$finish;

end

always @(clk1)

$display("%t: cout=\t%b\t%b", $time, clk_out, clk1);

endmodule

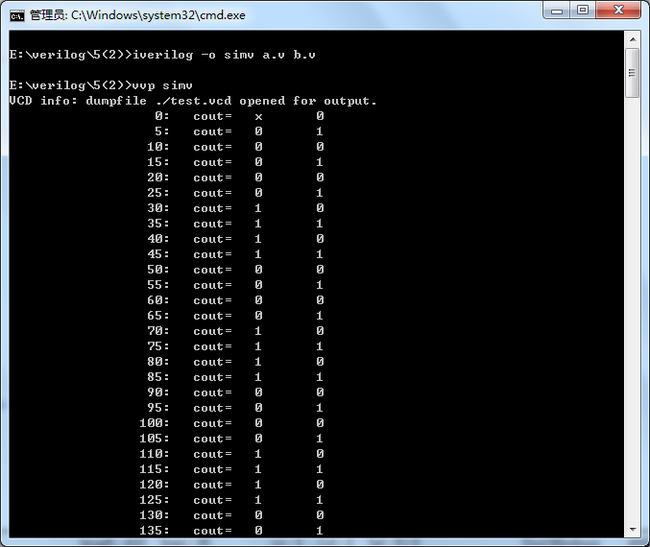

运行结果

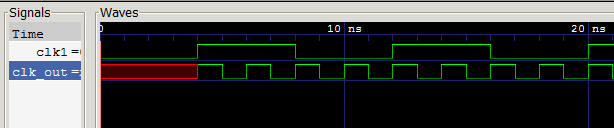

gtkwave.exe中显示的波形

二、将一个波形的频率减小4倍

设计一个周期为10ns的时钟clk1,占空比为50%,并设计一个模块,将clk1分为周期为40ns的时钟clk2

文件a.v代码

`timescale 1ns/100ps module clk_div_4(clk_out, clk1); input clk1; //输入时钟 input clr; //复位端 output clk_out; //输出分频时钟 reg clk_out; always @(posedge clk1) begin clk_out = 1; #1 clk_out = 0; #1 clk_out = 1; #1 clk_out = 0; #1 clk_out = 1; #1 clk_out = 0; #1 clk_out = 1; #1 clk_out = 0; end endmodule

文件b.v代码

`timescale 1ns/100ps

module test();

reg clk1;

reg clr;

wire clk_out;

clk_div_4 dut(.clk_out(clk_out), .clk1(clk1));

initial

begin

clk1 = 0;

end

always #4 clk1 = ~clk1;

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1,test);

$dumpon();

#100

$dumpoff();

$finish;

end

always @(clk_out)

$display("%t: cout=\t%b\t%b", $time, clk_out, clk1);

endmodule

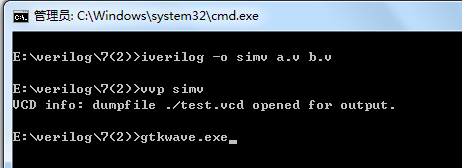

运行结果

gtkwave.exe中显示的波形

三、SRAM模型

设计一个地址宽度为8,数据宽度为8的SRAM模型

文件a.v代码

module sram_8_8(cs,rd,wr,address,din,dout); input cs,rd,wr; input [2:0] address; input [7:0] din; output [7:0] dout; reg [7:0] dout; //临时存储 reg [7:0] sram [0:7]; always @ (cs or rd or wr or address or din) begin if(wr == 1'b1) //写 begin if ((cs == 1'b1) && (rd == 1'b0)) sram[address] <= din; end else if(rd == 1'b1) //读 begin if((cs == 1'b1) && (wr == 1'b0)) dout <= sram[address]; end end endmodule

文件b.v代码

module test();

reg cs,rd,wr;

reg [2:0]address;

reg [7:0] din;

wire [7:0] dout;

sram_8_8 dut(.cs(cs), .rd(rd), .wr(wr), .address(address), .din(din), .dout(dout));

initial begin

cs <= 1;

rd <= 0;

wr <= 1;

address <= 3'b010;

din <= 8'b00011011;

# 50

rd <= 1;

wr <= 0;

# 50

rd <= 0;

wr <= 1;

address <= 3'b011;

din <= 8'b00011010;

# 50

rd <= 1;

wr <= 0;

end

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1, test);

$dumpon();

#200

$dumpoff();

$finish;

end

endmodule

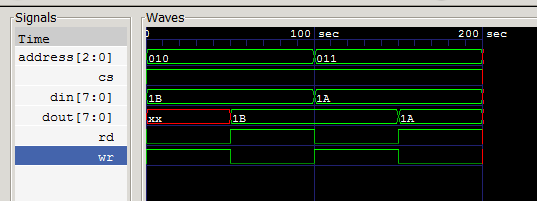

运行结果

gtkwave.exe中显示的波形

END