【FPGA开发】Modelsim和Vivado的使用

本篇文章包含的内容

- 一、FPGA工程文件结构

- 二、Modelsim的使用

- 三、Vivado的使用

-

- 3.1 建立工程

- 3.2 分析 RTL ANALYSIS

-

- 3.2.1 `.xdc`约束(Constraints)文件的产生

- 3.3 综合 SYNTHESIS

- 3.4 执行 IMPLEMENTATION

- 3.5 烧录程序

- 3.6 程序固化

-

- 3.6.1 SPI约束

- 3.6.2 `.bin`文件的产生

- 3.6.3 `.mcs`文件的产生

- 3.6.4 添加配置的存储器件并配置固化文件

笔者在这里使用的Vivado软件版本是Vivado 2020.2,据说该版本比较稳定。参考的课程是正点原子的课程手把手教你学达芬奇&达芬奇Pro之FPGA开发篇。文章未完成,但是会不定期补充完善,笔者学到新的Vivado使用技巧和操作也会更新到此文章中,如果篇幅过大就单独写一篇文章说明。

一、FPGA工程文件结构

首先说明一下FPGA工程的文件结构,一个科学的文件结构对于工程的管理和维护是十分重要的。笔者使用的文件结构如下:

- Doc:存放说明性文件,例如模块功能框图,芯片的参考手册,波形图,README文件等。

- Sim:存放仿真相关文件,例如TestBench文件,Modelsim工程文件夹使用的仿真模块等。

- TB:存放TestBench文件。

- 存放Modelsim仿真的文件等。

- Rtl:存放工程中所有模块的Verilog源码(RTL代码)。

- Prj:Vivado工程文件夹。

二、Modelsim的使用

较为简单,暂略,之后有时间再补充。

三、Vivado的使用

3.1 建立工程

- 工程的名字一般和顶层模块的名称保持一致,将工程文件的位置确定为

Prj文件夹后取消勾选Create project subdirectory。 - 选择RTL Project。

- 添加RTL源文件(Verilog代码)。

- 添加约束文件(可以在工程内手动添加)。

- 选择FPGA芯片型号(达芬奇为xc7a35tfgg484-2)。

3.2 分析 RTL ANALYSIS

点击Open Elaborated Design对代码进行RTL分析。在右上角的菜单中可以原则不同的分析视图:

- Default Layout:打开默认布局(代码的逻辑原理图)。

- I/O Planning:IO管脚约束,打开之后可以在下面的

IO Ports窗口约束管脚及对应的电平标准。按快捷键Ctrl+s保存后会弹出一个窗口,要求建立管脚约束的.xdc文件。.xdc文件的文件名一般和顶层模块名(工程名)保持一致。.xdc文件也可以自己编写,利用相关资料直接在该文件中写约束管脚的代码实现的效果是一模一样的。 - Floorplanning

分配完IO管脚约束之后就可以点击生成比特流文件了,点击后自动完成综合(Synthesis)和执行(Implementation)操作。

3.2.1 .xdc约束(Constraints)文件的产生

.xdc约束文件可以由上面的方法产生,也可以在Source窗口直接点击鼠标右键产生。

3.3 综合 SYNTHESIS

所谓综合,就是将Verilog的逻辑代码对应到FPGA的底层硬件的操作。在分析(RTL Analysis)中打开的原理图是一个抽象出的原理图,而在综合中打开的原理图是和FPGA的硬件资源直接相关的原理图。

3.4 执行 IMPLEMENTATION

在执行(Implementation)中可以查看实际的硬件电路连接图。

3.5 烧录程序

点击PROGRAM AND DEBUG中Open Hardware Manager中的Open Target进行自动连接,Vivado会自动识别生成的比特流文件.bit。点击下载Program即可下载程序。

3.6 程序固化

通过3.5的在线烧录的方法是无法将程序烧录到板卡上去的,只有将编译好的程序烧录到开发板上的 QSPI Flash 中,程序才能上电后自动执行。QSPI中的Q是指该芯片的数据线有4位,分别是DQ0~DQ3。达芬奇上的Flash除了可以存储程序外,还可以存储一些用户数据。

固化烧录文件主要分为以下两种,它们都可以由比特流文件.bit产生:

.bin文件:一般由Vivado软件编译产生,存储在特定目录下的二进制文件.mcs文件:一般通过Vivado GUI界面操作或TCL命令生成,.mcs文件里包含了.bin文件的内容,除此之外,每行的开始有地址信息,最后一个Byte是CRC校验信息。

3.6.1 SPI约束

对于达芬奇开发板而言,在工程的.xdc文件中添加以下约束以加快上电后的程序读取速度。

# SPI Configuration

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

# 所有未使用的引脚都上拉

# set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design]

3.6.2 .bin文件的产生

在Settings中找到Bitstream,勾选-bin_file按钮即可在每次生成比特流文件.bit后生成对应的.bin文件。生成的两个文件可以在以下目录中找到:

../Prj/project_name.runs/impl_1/

3.6.3 .mcs文件的产生

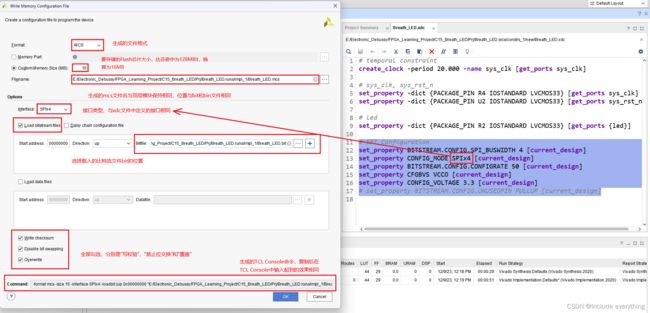

点击菜单栏中的Tools,点击Generate Memory Configuration File…打开以下窗口:

3.6.4 添加配置的存储器件并配置固化文件

打开Open Hardware Manager并连接好器件后,点击菜单栏中的Tools,点击Add Configuration Memory Device并选择器件型号,打开以下窗口:

依次选择制造商,大小,通信种类和位宽,下面的搜索栏中就会出现对应的器件。在这里(达芬奇)出现的两个器件,上面的是3.3V的,下面的是1.8V的,故选择上面的即可。

选择OK后,跟随引导窗口配置固化文件。如果没有跳出窗口,也可以在Hardware窗口右击选择Program Configuration Memory Device…打开配置窗口:

选择任意方式生成的固化文件均可,选择后其他选项保持默认(擦除,下载程序并校验)点击OK就会自动开始下载,重启开发板电源即可看到对应的程序现象。如果只需要擦除就仅选择Erase即可。

持续不定期更新完善中……

原创笔记,码字不易,欢迎点赞,收藏~ 如有谬误敬请在评论区不吝告知,感激不尽!博主将持续更新有关嵌入式开发、FPGA方面的学习笔记。