AXI3与AXI4区别及互联

AXI3与AXI4区别及互联

------------------------------------------

版权声明:

本文作者:烓围玮未。主要从事ISP/MIPI/SOC/车规芯片设计

首发于知乎专栏:芯片设计进阶之路

同步微信公众号:芯片设计进阶之路(x_chip)

转发无需授权,请保留这段声明。

------------------------------------------

前言:在SOC各种总线中,AXI是最重要的总线,没有之一。不管是在工作中,还是在面试中,AXI协议是一个必须精通的知识点。ARM 从AMBA1到AMBA5一共五代的AMBA总线中,AXI有两代,分别是AMBA3 的AXI3和AMBA4的AXI4。AXI3和AXI4的区别在协议里当然可以找到对应的部分,但是真正的理解和总结AXI3和AXI4的文章确实没有找到。这篇文章结合自己的理解来总结一下AXI3和AXI4的区别以及互联。

另外,说一句题外话,如果想真正的理解AXI总线,那么必须要去学习CPU和SOC体系结构的相关知识,因为AXI作为系统总线很多功能就是为系统来服务的。

1. AXI3与AXI4的区别

为了方便总结和记忆,AXI3和AXI4的区别的思维导图如下:

1.1 Burst support

AX4对burst length进行了扩展:

- AXI3最大burst length是16 beats;AxLEN位宽是4bit

- AXI4支持最大到256 beats,AxLEN位宽是8bit;但是这也是有限制的:

1. 只有INCR burst type支持超过16 beats的Burst;WRAP and FIXED burst types 最大还是支持16 beats的Burst,和AXI3保持一致;

2. Exclusive accesses 的burst length 必须小于 16.

但是在实际使用中,很少使用支持超过Burst Length超过16的命令,这是因为Burst Length太长会一直占用总线,影响了系统性能;而且AXI总线的一个限制就是Burst一旦开始是不能取消的,如果Burst太长,一旦出错,影响比较大;

比如在ARM的CPU中,就没有使用超过16 beats的Burst。

1.2 Quality of service signaling

- AXI4 增加了2个4-bit QoS 命令信号:

AWQOS 4-bit QoS identifier sent on the write address channel for each write transaction

ARQOS 4-bit QoS identifier sent on the read address channel for each read transaction.

但是AXI4协议并没有规定QoS的用法,也规定不了,因为这是一个系统全面考虑的特性。AXI4协议不可能规定某个master比如CPU必须是多少QoS,这和SoC的系统实现强相关,一般是架构师会定义。

AXI4建议的QoS是AxQOS值越大,优先级越高;但是要注意的是,有些SoC恰恰相反,AxQOS值越大,优先级越低,所以要根据Spec来;

QoS信号的增加是随着越来越多的master对总线需求的冲突越来越明显,系统的带宽就那么多,那么如何给不同的IP分配不同的QoS就是一个架构师必备的功底,而且没有不变的规律可以遵守。

1.3 Multiple region interfaces

- AXI4为了支持区域标识,增加了两个4-bits的区域标识符:

AWREGION region identifier sent on the write address channel for each write transaction

ARREGION region identifier sent on the read address channel for each read transaction.

- 区域标识符的使用意味着slave不必支持不同逻辑接口之间的地址解码。

如果一个slave把内部可访问地址分为多个区域,那么一般情况下,只需要通过高位地址来区分不同的区域;如果采用了区域标识符,那么就不需要采用地址解码区分了。

另外,通过划分region,对某些physical allocation进行保护,别如某个region只能被non-secure write,某个region只能被secure write访问;

- 这是一个可选的功能,一般用的比较少,而且ARM自己的CPU都很少支持。

1.4 Write interleaving

AXI4协议去掉了WID信号,因此不再支持write interleaving。这是AXI4和AXI3的很重要和很大的一个改变。

Write interleaving的去除使得在WID信号上传递的信息是多余的。所有写入数据必须与相关的写入地址顺序相同,任何需要WID信息都可以从写入地址通道信号AWID中获得这些信息。

- Write interleaving如下图所示:

- 在AWID=0的数据还未发送完后,允许AWID=1的数据先发送;

- 这样带来的代价是发送端必须要缓存多个ID的wdata,不管是maser还是总线interconnection都必须要增加大量的缓存,所以增加了面积;

- 另外,Write interleaving增加了系统总线设计的复杂度,而且很容易造成死锁,所以虽然AXI3支持Write interleaving,但是大家在设计的时候,master基本都没支持Write interleaving。

- 所以AXI4就把Write interleaving的支持去掉了。

1.5 Write response dependencies

- AXI4对Write response的产生做了更严格是限制。

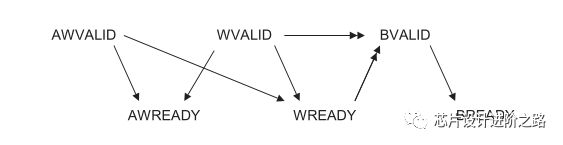

- AXI3 BVALID的产生依赖关系如下:

- AXI3必等到了WVALID和WREADY后才能把BVALID置高来响应,也就是说只要收到了所有数据,SLAVE就可以发写响应。

AXI4规定,必须等到AWVALID,AWREADY,WVALID, WREADY, and WLAST 都为高(不是同一时刻都为高)后,SLAVE才能发BVALID进行写响应。也就是不仅仅要等数据通路,而且要等地址通路,并且明确了要等WLAST。这样能保证响应的时候Transaction是真正完成的。

AXI3对BVALID的规定其实是有漏洞的,可能Transaction还未真正完成就发送了写响应。AXI4的更新更加合理和严谨。

1.6 User signals

- AXI4增加了user信号:

AWUSER Write address channel User signals.

ARUSER Read address channel User signals.

WUSER Write data channel User signals.

RUSER Read data channel User signals.

BUSER Write response channel User signals.

AMBA4中并未对USER信号做任何规定,只是建议不要使用这个信号,防止IP直接互联不兼容。但是实际soc中,这个信号使用的还是比较多的,用来传输sideband信号十分有用。

AMBA5中进一步规定了USER信号的位宽:

所以说,这个信号在SOC内部使用比较多,但是如果要和外部互联,比如IP 厂商一般都不会使用,防止兼容性问题。

1.7 Locked transactions

This section describes the removal of locked transaction support in AXI4.The AXI4 signals effected are AWLOCK and ARLOCK.

AXI4去掉了对locked transaction的支持,对信号的影响就是AxLOCK从AXI3的2-bits减少到了1bit:

- 如上图所示,AXI4去掉了Locked access。

为什么会去掉Locked access,这是因为Locked access不好用,当然这是废话。Locked access和Exclusive access的区别是作用的对象不同。

- Locked access作用的对象是总线,一旦发生Locked access,那么其他的master都不能使用总线了。在一个复杂的SOC系统中,Locked access对系统的影响就太大了,万一发生Locked access的master出点啥问题,整个系统就挂死了。这种牺牲整个系统来成就某个master的机制当然就会被抵制,最后AXI4直接不再支持这种方式。

- Exclusive access 作用的对象是对应的Slave,支持Exclusive access的Slave会在slave中实现一个Exclusive access monitor,如果monitor记录了能够访问的master,那么对应的master就能通过Exclusive access来访问,其他的未记录的Exclusive access就都不能访问。Exclusive access对总线系统是没有要求的,只是对slave做了特殊要求,即使出错也不会影响系统其他部分,最多访问失败而已。

现在一般的AXI master都不会支持Locked access,如果一个IP支持Locked access,大概率没人会买它了。对系统来说不仅实现麻烦,而且还存在挂死系统的风险。

1.8 AWCACHE and ARCACHE

- AXI4的AWCACHE[3:0] 和ARCACHE[3:0]的含义有很大的改变,

- AXI3 中AWCACHE[3:0] 和ARCACHE[3:0]的含义如下图所示:

- AXI4中AWCACHE[3:0] 和ARCACHE[3:0]的含义如下图所示(括号内的是AXI3的编号):

AWCACHE[3:0] 和ARCACHE[3:0]的属性的改变主要是有用ARM CPU架构的演进,定义的memory属性越来越多,越来越复杂,所以对AWCACHE[3:0] 和ARCACHE[3:0]的解释就越来越多。这些和CPU的架构,还有CPU存储系统有很大的相关性,这里就不详细解释了,如果要深入理解,必须去学习ARM CPU V8架构才行。

1.9 AXI-Lite

AXI4相对于AXI3的另外一个改变就是定义了AXI-Lite协议。lite协议其实主要目的是简化protocol,用于系统上对register的访问,在实际工作中接触的比较少,这里就不详细解释了。

2. AXI3和AXI4的互联

上面介绍了AXI3和AXI4的主要区别。实际SOC中,有些IP是AXI3接口的,有些IP是AXI4接口的,那么这些不同AXI版本之间的互联需要注意什么呢?可以分成下面两种情况:

2.1 AXI4 Master连接到AXI3 Slave

- AXI4 Master连接到AXI3 Slave要注意以下几点:

1. 由于AXI4是没有WID信号的,不能直接把AXI4 Master的AWID直连到AXI3 Slave 的WID上,这是由于如果AXI4 Master能够发出outstanding的命令,当前AWID值和当前的WID值就不是同一个了。通常的做法是把AWID都存到一个FIFO中,等到数据传完了(WLAST收到了)再切换到下一个AWID. 把这样读出的AWID作为WID使用。

2. AXI3的AxLOCK信号是2-bits的,做法就是直接将AxLOCK[2:0](slave) = {1’b0, AxLOCK(master)}即可。

3. AXI4 Master不能产生超过16beat的burst,通常也不会,但是要注意;

4. 系统总线要么统一用AXI3, 要么统一用AXI4;

5. AXI3 Slave必须注意BVALID的产生要符合AXI4协议,需要修改逻辑,一般也不会有问题。

6. QOS/USER/REGION信号等多余的信号需要做额外的处理。

2.2 AXI3 Master连接到AXI4 Slave

1. 由于AXI4是没有WID信号的,所以直接把WID Floating就行;

2. AXI4 Slave的AxLOCK[0] = AxLOCK[0](slave)即可;

3. AXI4 Slave的AxLEN[7:4]=4’h0 即可;

4. 系统总线要么统一用AXI3, 要么统一用AXI4;

5. QOS/USER/REGION信号等多余的信号需要做额外的处理。

6.AXI3 master必须不能支持Write interleaving,否则必须修改AXI3 master

上面这些就是AXI3和AXI4互联的一些注意事项,在实际的工作中,很多IP都是AXI3兼容AXI4的,可以减少一些工作。否则就必须做AXI3和AXI4协议转换逻辑了。

后记

AXI总线是SOC芯片设计最重要的总线,没有之一!可能很多刚入门的工程师即使把协议读了很多次,还是不能深入理解。这是因为,ARM 没有告诉你,需要你去了解CPU架构,了解cache,了解存储系统,了解系统架构等等知识。只有了解了这些知识才能理解USER/QOS/AxCACHE等信号的具体作用,因为AXI总线本来就是为了解决系统互联而产生的。

技术很重要,技术背后的思想更重要!

技术背后的某些思想就是你解决以后问题的钥匙。希望本文对你有一点点帮助。

赠人玫瑰,手有余香。原创不易,如果你有所收获,可以关注我的知乎专栏和微信公众号,不定期更新文章。谢谢!

PS:最近颈椎不舒服,所以很久没更新专栏了,最近好一点了,慢慢更新,见谅!

知乎专栏:芯片设计进阶之路

微信公众号:芯片设计进阶之路 x_chip

——————————————————————————————————————