数字IC后端设计如何从零基础快速入门?(内附数字IC后端学习视频)

数字IC后端工程师是做什么的?

数字IC后端工程师主要职责是把数字IC前端工程师写的逻辑功能RTL转变成物理实际连线GDS版图。这个过程的本质是基于一定的时序约束和物理约束将设计的逻辑功能等价转变成物理连接。因为这个GDS最后是要提交给foundary进行芯片加工制作的,光刻机无法识别逻辑功能,它只认一层层的物理实际连接。

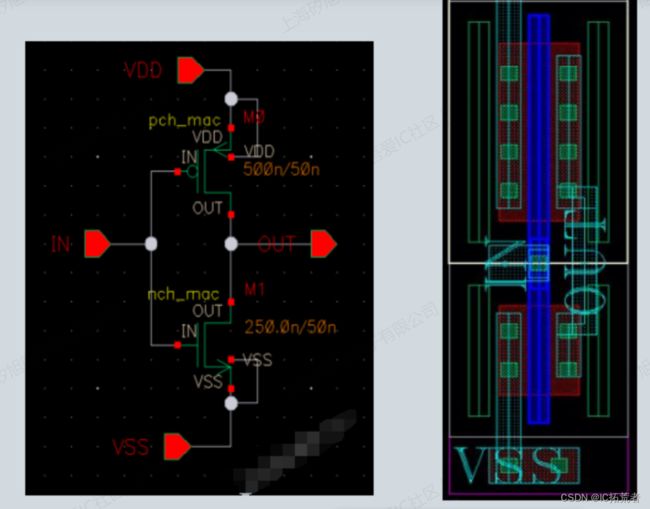

以上面反相器为例,左侧为电路图,右侧为对应的版图GDS。实际芯片的电路图是一个比较复杂的设计,我们的目的就是把复杂的原理图变成等价的物理版图GDS。

物理版图以GDSII的文件格式交给台积电这样的芯片代工厂,在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了我们实际看见的芯片。

只不过在做等价转换的过程,我们需要既要确保时序(setup,hold,transition)符合foundary规定的signoff要求,也要确保我们画出来的物理版图GDS的金属和base layer连接符合foundary工艺制作的规则。因为时序不满足芯片的性能无法保证,设计规则不满足foundary加工制作可能会出现错误,比如不同的两条连线搭在一起做成一条线了。

行业入门定义

经常也有小伙伴们说我已经入门了,但只会跑flow,点下runall就结束了,不知道如何看log和report。其实这种情况并非真的入门了。

那要达到什么样的状态才是真的进入数字IC后端实现的大门呢?小编从自己的角度给出以下几个指标,大家可以自己评估下。

1了解数字IC后端实现中的各种基本概念

基本概念训练营上都有。遇到一些不太理解的概念,大家可以提问。这些概念面试时经常会被问到。

2 熟悉整个数字IC后端实现流程(从PR到PV)

我们的训练营包含了整个全流程。从综合后的netlist一直到物理验证的DRC和LVS clean。在公司实际项目,我们做完这些后是可以直接拿着GDS去流片的(Tapeout)。先从理论上了解整个设计流程,了解每个流程都是做什么工作。然后结合我们服务器上的flow,边做边理解,对flow中的主要命令争取做到知道它们的内涵。

3 熟悉各个阶段的步骤及意义

我们也提供了数字IC后端设计实现ICC2和Innovus每个阶段的log解读,建议大家结合这个来了解学习每个步骤都包含哪些内容,以及思考为何工具要这么做。

4 熟悉看懂timing report

虽然说数字IC后端工程师更侧重physical实现,但必须要有时序timing的基础,遇到数字IC后端实现过程中遇到的时序问题,要学会分析问题,找到root cause并解决掉问题。

对于timing report的解读我们也有相关的教程。这个必须学会看。反正一点都不难。

5 熟悉Timing/Congestion/Route的基本优化方法

这个训练营上也有很多教程和专题案例阐述这些主题。建议好好理解下这些文档。每个主题都包含了一系列的知识点以及实战经验总结。刚好这些都是面试要被问到的。

如果在面试过程中能与面试官分享我们的这些方法,那拿个speical offer一点问题都没有。讲真,只要你认真学习研究我们训练营中任意一个案例专题分享,面试过程把这个技能展现出来,今年的offer至少是40万+(上海数字中后端岗)。

6 会编写简单TCL脚本

数字IC后端训练营也提供一些TCL脚本。比如关于模块面积估算等脚本,可以拿来学习下。小编知识星球提供了无数个实际项目的应用脚本,随便拿出一个脚本来练习即可。0基础只要掌握一些很基本的TCL写法就可以。

学习脚本核心要点:多看,多抄,多写!(大学阶段都有抄作业的经历吧,照着来就对了!)

7 独立完成简单block的整个实现流程

0基础建议优先选择Innovus flow。Innovus的GUI界面做的比较好。对于一些初学者来说,往往他们喜欢通过界面的操作方式来学习和做项目。而ICC2在这方面做的确实没有Innovus好。因为很多脚本命令在GUI中是找不到的,而且即便有的有对应界面操作,但是选项一大堆,无法无脑操作。

整个数字IC后端设计实现PR flow是为了做出一个符合timing signoff和physical signoff标准的数据。其中timing signoff包含setup time,hold time,removal,recovery,max transition,max cap等都要符合设计的spec。

比如我们IC训练营项目要求频率至少跑到900MHz,timing drv要满足TSMC的timing signoff要求。

而physical signoff主要是包含DRC,LVS和IR Drop等方面,要求它们都要clean并符合signoff要求。

为了达到这些目的就需要在PR阶段能够尽量让工具自动来帮我们实现这些目的。这些事情就是PR flow要做的事情。当然工具毕竟还是机器,它不了解我们的设计,肯定无法满足我们的所有需求。但工具本身的功能是很强大的,因此我们需要在flow中引导工具来实现我们所需要的效果。

比如某个局部区域有high pin density的cell,我们可以人为给这个区域的这类cell加cell padding来改善消除local congestion。

手把手教你如何在Innovus中解决local congestion问题

比如route后发现DRC有很多,经过分析后发现是cell density太高导致的,那我们可以适当扩点面积,重新跑flow做优化。而面积够不够这个工具并不会直接告诉你,而是需要大家借助工具的一堆report和其他经验来做判断的。

比如工具默认是按照时钟来划分timing group的,往往优化出来的timing不是很理想。如果我们把这些group做细化,划分成很多timing group,并给每个group添加不同的effort来进一步优化改善时序。

比如某个阶段timing突然变差很多,工具也仅仅会输出一个timing report。它并不会帮你去分析每个阶段间timing的差异性,更不会直接打印一些关于如何来优化timing的建议信息。这个分析需要工程师自己去分析,然后再把一些改进的方法加入到flow中。

比如之前分享的ctsopt后timing突然变差的案例,其实就是工具默认采用了useful skew导致的。如果分析到是这个原因导致的,我们就可以通过optMode的设置来告诉工具不要有这样的行为,从而解决掉这个问题。

数字IC后端工程师岗位所需IC技能树

1懂设计本身

对于数字后端工程师来说,一般是不会去写代码,但必须要懂设计。比如你作为一个chip的top owner,做后端实现时你必须根据设计的data flow,各个模块之间如何交互,各个时钟之间的关系等信息来规划floorplan,做好标准单元的摆放,时钟树综合等工作。

如果你对设计本身不清楚,那么你就是硬着头皮做数字IC后端,你一定会做得很累,很痛苦。经常碰到很多工程师抱怨timing太难收敛了,绕线总是绕不开等现象。主要原因还是不懂设计,比如前端设计的时钟结构不合理,你仍然硬着头皮做,最后发现hold violation就是不好修,插入太多的holdbuffer,绕线又绕不通,陷入死循环。又比如placement后各个逻辑模块位置分布跟data flow不match,导致timing怎么都做不上去或者出现setup和hold打架(互卡)的情况。

2 懂逻辑综合

熟悉逻辑综合各个阶段(逻辑优化,DFT等)工具都做了哪些工作,每个工作对数字后端实现可能造成的影响。

需要与前端工程师沟通,了解设计架构,时钟电路结构,各个时钟间的同步异步关系,芯片的应用场景等方面。

根据设计需求编写设计约束文件SDC并请前端设计工程师review(这个过程需要不断与前端设计工程师不断沟通,特别是第一次做某个新的design)。

制定扫描链插入方法,分配scan chain条数,确保测试覆盖率,产生scan test pattern。

根据数字后端实现情况决定是否需要做scan chain reordering。熟悉scan chain reordering的工作机理,对hold的影响。

熟练掌握DCT/DCG的逻辑综合flow,以及哪些设计需要做DCT/DCG。甚至如果你对设计和工具的行为有足够的熟悉,完全可以用DC+DCT的混合模式来实现设计需求。

理解综合工具的行为,高效率fine tune 综合阶段和布局布线阶段之间的timing一致性。掌握一系列可以改善timingcorrelation的方法,比如set_max_cell_density等变量的设置,以及如何反馈PR阶段的clock latency给综合工具等等。

3 精通布局布线(Place&Route)

工艺选择

对于一个新工艺可以快速评估当前项目需要选用某个工艺节点的哪个metal stack,是1P7M还是1P8M?是用9Track还是12Track?这个选择涉及到数字后端powerplan规划,IR drop,布线阶段可用的绕线资源,封装形式,乃至整个芯片的成本。

IP相关

需要根据设计需求和后端floorplan,与IP vendor沟通定制IP的形状和orientation。这里简单提一下,很多工程师经常犯一个错误就是IP的poly orientation问题。比如vendor提供给你的是EW方向,而你做floorplan时确把它当做FN来使用(这点是致命的)。

能够从IP Vendor提供的文件中快速提取check list。比如IP和core logic之间应该预留多少spacing,IP中某些关键信号对电阻的特殊要求等等。

能够给IP规划一个robust的powerplan。很多工程师还只是停留在将IP的power ground pin连起来,而忽视供电robust特性。小编反正每次都是将power net能画粗点就尽量画粗点,能形成power mesh的就尽量画一个电阻最小的power网络。总之powerplan一定要经得起review。

模块partition

chip或者block 形状选取(矩形或者方形抑或多边形,与design相关,关乎routing 资源)。深知各个block的难易程度,各个模块适合用什么类型的形状等。

能够根据数字IC后端实现情况,向前端提出那部分逻辑可能需要单独做hardening。因为前端对于模块的切分可能仅仅考虑逻辑功能方面,而后端则可以根据实现的复杂程度和难易程度,反馈可能需要单独做PD的模块。

根据design的data flow,合理摆放各个partition模块的位置以及出pin位置。为了节省面积,经常还需要做信号的feedthrough,实现模块之间无缝对接(channeless)。对于低功耗设计,可能还需要提前规划若干个孤岛,用来走某些特殊的signal或者clock。

chip area面积 估算

为IO添加core vdd &core vss以及IO vdd& IO vss。前者涉及芯片功耗的估算,后者设计SSO的计算。同时还需要考虑ESD和EM。

IO添加完成后,根据各个模块的面积,IP的面积,IO的面积就可以大致估算是chip的面积。这里需要指出的是,如果chip是IO limited,则可以反馈信息给PM,询问是否可以通过IO mux来实现IO的复用,从而减少IO的数量。如果chip是core limited,则需要重点将各个子模块的面积最到最小。

Timing,功耗Power,面积,congestion优化

Timing优化贯穿着整个数字IC设计全过程。一个对设计比较了解的工程师,一定可以做好timing优化,它可以站在设计的角度来规划模块的分布。PR数字IC后端实现阶段用于优化timing的一些方法如下:

使用SPG flow

使用Multi-Vt 作为target_library优化

CCD flow

create_voltage_domain, create_bounds,keepout setting,group_path等

对于设计实现中碰到的congestion问题都能快速找到root cause,从根源上解决。

Power功耗优化

低功耗设计flow和方法论

掌握优化leakage和动态功耗的方法

时钟树优化

这个阶段需要数字IC后端工程师能够自己来分析时钟树结构,并根据design的spec来编写一个约束文件,引导工具 如何长时钟树。很多SOC中,时钟都有几百个。由于PLL的个数有限,因此很多设计都有时钟选择和切换电路。因此,针对复杂的时钟结构,工具可能很难做到符合我们预期的时钟树(clock skew 和clock latency)。

很多数字后端工程师经常担心自己的工作会被工具所替代,其实大可不必。有这方面担忧的朋友可能做的是假后端,可能仅仅停留在run flow这个层次。小编从来没碰到过工具能把复杂模块的cts自动做好的,人为干预的东西真的是不要太多了。难道你们不觉得工具真的很笨吗?

这步非常关键且非常重要,也是衡量一个数字后端工程师能力的重要指标。主要工作如下:

clock tree building constraint的编写

长时钟树需要设置的timing drc等

时钟树用于长tree的buffer或者inverter种类选择

时钟树的ECO

设定clock net 的non-default rule

如何做shielding,对哪些net可以做shielding,影响是什么

绕线和串扰SI

熟练掌握fix short的方法

理解SI产生的原理和避免SI的方法

理解SI和noise的区别(见知识星球上解析)

4精通Function ECO

不论是pre-mask或者是post-mask,都可以高效完成设计所需的FunctionECO。这里涉及ECO所能动用的layer,是通过用ECO cell还是spare cell来实现,ECO后的timing fixing,LVL比较,利用ECO CELL和Space CELL做function eco各自的优缺点等。

5 IR Drop分析和优化

精通IR Drop分析和优化包括静态和动态IR Drop分析。对一个chip分析IR drop后还需要对其进行优化。对于基于Redhawk的IR Drop分析flow之前已经在知识星球上分享过。IR drop优化的方法也分享过无数次了。

IR Drop分析之Redhawk分析流程

数字IC设计后端实现前期预防IR Drop的方法汇总

6 理解各大EDA工具

工具一定不是万能的,bug也是无处不在,但是如果你能将工具的长处用的淋漓尽致,那么你一定会喜欢上它的。一方面资深的后端工程师懂得工具的局限性,工作时尽量避免工具进入此工作模式,不掉入“陷阱”中。另外一方面对工具的行为有比较透彻的理解,可以利用工具为我们所用,可以利用它的特性来guide工具实现我们的需求。

7 精通时序分析和timing signoff

时序分析和timing sigoff这步,很多数字IC后端工程师也都做了。但是你是否是拿着现有的flow跑下primetime,然后就开始你的leakage optimization,hold violation fixing 和timing drc的fixing?这个能力是每个数字后端工程师都必须具备的,但是仍然远远不够。你需要搞清楚以下几点:

signoff的标准,如何定?(特别是一个新的工艺)

如何优化leakage优化的flow,使得leakage最小化?

如何少插hold buffer?

遇到hold buffer修不进去,如何解决?

数字IC设计中ECO的那些事,其实并不是事!

8 精通物理验证

这步属于数字IC设计中的physical signoff阶段。主要为DRC,LVS,ERC,ESD,Latch up 等方面的检查和修正。在先进工艺节点中,physical vertification显得更为重要。

LVS 就是这么简单!(数字后端物理验证篇)

9 精通脚本语言

脚本能力强,至少掌握一种及以上脚本语言(TCL,perl,python等)。至于哪种语言不重要,关键是要学会一门语言并且能够熟练运用。

9 涉面广且有专长

面广就比如本篇所列到甚至更多方面你都比较熟练。专长是指你至少要在某个领域有深入的研究而且做的要比别人好,比如擅长做高频率的模块实现,或者擅长physical方面(powerplan,DRC ,LVS等),抑或擅长写脚本,能够写一个timing engine出来。

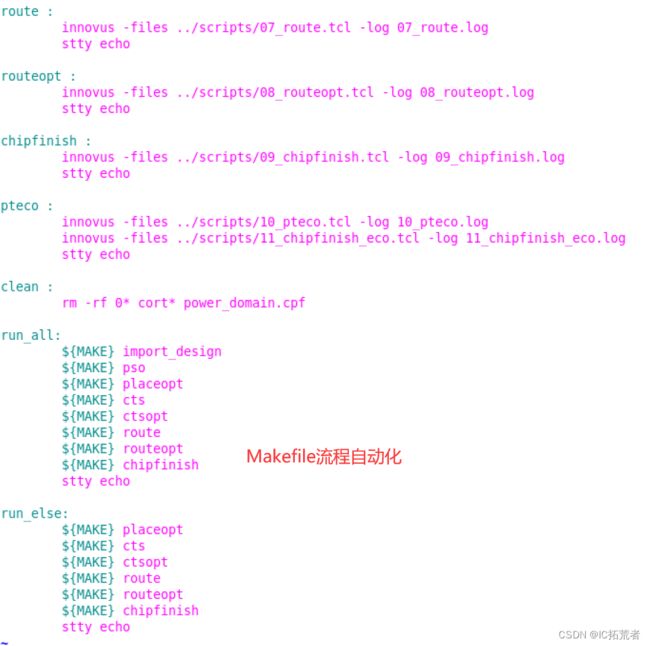

10流程自动化

将整个实现flow(从综合到物理验证)调好后,一旦rtl ready后可以自动一键实现从RTL到物理验证(较少的DRC)。

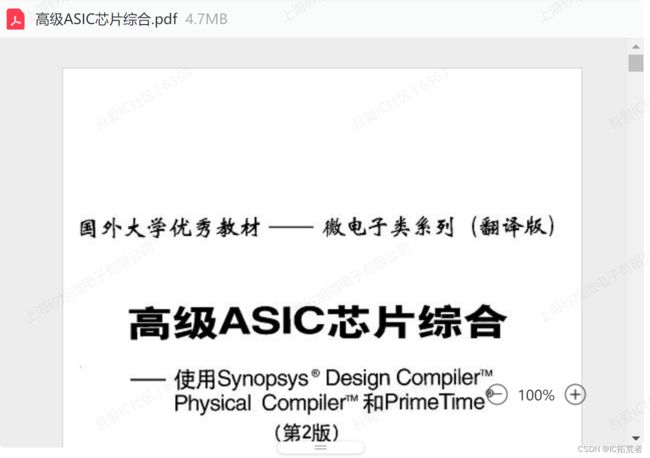

数字IC后端设计书籍推荐(数字IC后端学习资料)

吾爱IC社区小编作为一线12年数字IC后端工程师,今天推荐几本数字IC后端相关书籍给大家。每本书都有电子版本,有需要可以找小编免费领取。

数字集成电路物理设计

高级ASIC芯片综合

静态时序分析STA经典红宝书中文版

集成电路静态时序分析与建模

低功耗设计方法论Methodology

数字IC后端设计实现培训视频免费观看下载

吾爱IC数字后端训练营