计算机组成原理课设

目录

注意!

1 实验0:ROM仿真

1.1 实验目的

1.2 原理设计

1.3 结果验证

2 实验1:验证74LS181运算和逻辑功能

2.1 实验目的

2.2 原理设计

2.3 部分结果验证

3 实验2:运算器(2)

3.1 实验目的

3.2 原理设计

3.3 部分结果验证

4 实验3:字发生器及跑马灯

4.1 实验目的

4.2 原理设计

4.3 部分结果验证

5 实验4:模拟微程序实现指令

5.1 实验目的

5.2 原理设计

5.3 部分结果验证

注意!

内容均是课设的相关知识,不要抄袭,在此只是学习笔记,给大家提供一些实现思路,希望大家理解所有实验的基本原理之后再进行自己的设计;

1 实验0:ROM仿真

1.1 实验目的

(1)掌握ROM的工作原理;

(2)画出逻辑电路图及布出美观整齐的接线图;

(3)掌握ROM读出原理。

1.2 原理设计

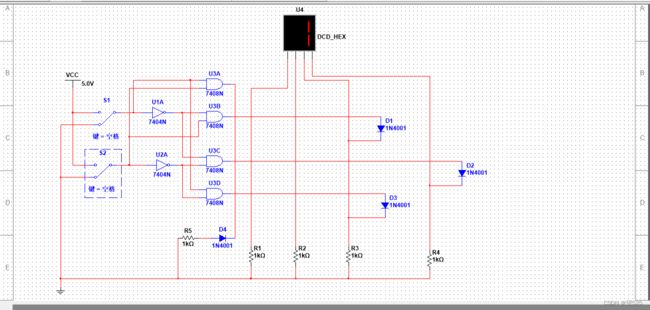

根据设计的需求(显示学号后四位,0000B,0010B,0001B,0010B)和电路原理(当电路上的二极管导通时,读数据为1,二极管不导通时,读数据为0),利用J1和J2两个开关控制四条数据线的选通情况,在每条数据线上用相应数量的二极管控制数据是1还是0,从而实现控制数码管显示相应的数字。

1.3 结果验证

1.J1和J2均为高电平,选通U3A,数据线为0,数码管读0,显示0;

2.J1为低电平,J2为高电平,选通U3B,数据线为2,数码管读2,显示0

2.J1为低电平,J2为高电平,选通U3B,数据线为2,数码管读2,显示0 3.J1和J2均为低电平,选通U3C,数据线为1,数码管读1,显示1;

3.J1和J2均为低电平,选通U3C,数据线为1,数码管读1,显示1; 4.J1为高电平,J2为低电平,选通U3D,数据线为2,数码管读2,显示2;

4.J1为高电平,J2为低电平,选通U3D,数据线为2,数码管读2,显示2;

2 实验1:验证74LS181运算和逻辑功能

2.1 实验目的

(1)掌握算术逻辑单元(ALU)的工作原理;

(2)熟悉简单运算器的数据传送通路;

(3)画出逻辑电路图及布出美观整齐的接线图;

(4)验证4位运算功能发生器(74LS181)组合功能

2.2 原理设计

该电路图分为四大部分,由两组开关和输入输出组成,左边的一组开关控制两个十六进制的输入信号,右边的一组开关从上到下分别对应S0,S1,S2,S3,CN和M,左边的两个数码管用来显示输入的两个十六进制数,最右边的数码管用来显示输出,通过控制控制右边的一组开关实现多种算术和逻辑运算。

2.3 部分结果验证

1.下图中设置S3,S2,S1,S0,CN,M分别为0,0,0,0,1,0进行算数运算F=数据1,输入数据1=AH,数据2=5H,输出F=数据1=A,符合逻辑功能; 2.下图中设置S3,S2,S1,S0,CN,M分别为0,0,0,0,0,0进行算数运算F=(数据1)+1,输入数据1=AH,数据2=5H,输出F=数据1+1=B。

2.下图中设置S3,S2,S1,S0,CN,M分别为0,0,0,0,0,0进行算数运算F=(数据1)+1,输入数据1=AH,数据2=5H,输出F=数据1+1=B。

3 实验2:运算器(2)

3.1 实验目的

(1)熟练掌握算术逻辑单元(ALU)的应用方法;

(2)进一步熟悉简单运算器的数据传送原理;

(3)画出逻辑电路图及布出美观整齐的接线图;

(4)熟练掌握有关数字元件的功能和使用方法。

(5)熟练掌握子电路的创建及使用。

3.2 原理设计

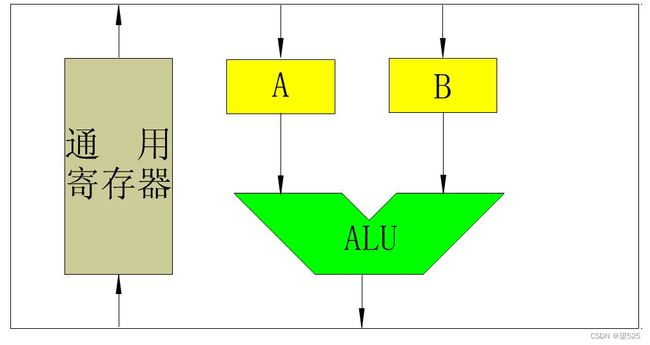

本实验仿真单总线结构的运算器,原理如图2-1所示。

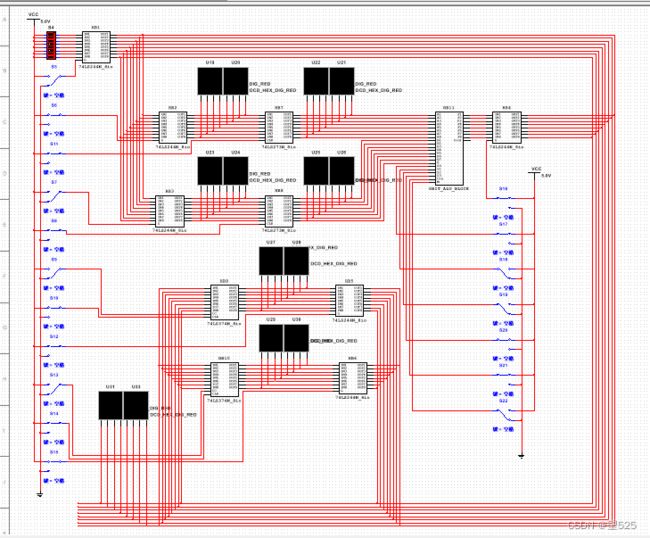

电路图中,上右下三方的8条线模拟8位数据总线;K8产生所需数据;74244层次块为三态门电路,将部件与总线连接或断开,切记总线上只能有一个输入;两个74273层次块作为暂存工作寄存器DR1和DR2;两个74374层次块作为通用寄存器组(鉴于电路排列情况,只画出两个通用寄存器GR1和GR2,如果可能的话可设计4个或8个通用寄存器);众多的开关作为控制电平或打入脉冲;众多的8段代码管显示相应位置的数据信息;核心为8位ALU层次块。

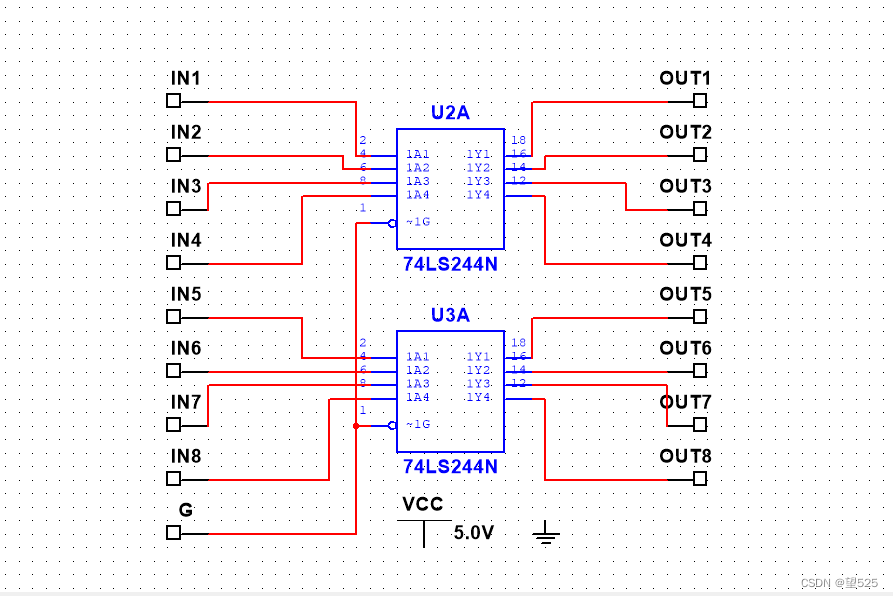

1.自定义9输入,8输出的74LS244N层次块;

2.自定义9输入,8输出的74LS273N层次块;

3.自定义10输入,8输出的74LS374N层次块;

4.实验电路图;

3.3 部分结果验证

(1)K8产生任意数据存入通用寄存器GR1:将S6也就是k8的74244接地,将数据放BUS,将GR1的OC置为低电平,然后将CLK由低电平变为高电平,将数据存入到GR1中,然后将S6的74244置为高电平。

(2)K8产生任意数据存入通用寄存器GR2:将S6也就是k8的74244接地,将数据放BUS,将GR2的OC置为低电平,然后将CLK由低电平变为高电平,将数据存入到GR2中,然后将S6的74244置为高电平。

(3)完成GR1+GR2→GR1:将GR1的OC端接地,将GR1的74244接地,把数据放到BUS上,将DR1输入端的74244接地,然后控制CLK端由低电平变为高电平,将数据存入DR1,将所有的74244接高电平,同理将GR2中的数据存入DR2中,将8位ALU的控制端S3,S2,S1,S0,CN,M分别置为1,0,0,1,1,0然后ALU将DR1和DR2相加的结果输出到F1-F8中,将8位ALU的输出74244三态门接地,将数据放到BUS上,然后将GR1的OC门接地,将CLK由低电平变为高电平将数据存入GR1;将对应的74244门接高电平。

4 实验3:字发生器及跑马灯

4.1 实验目的

了解字发生器的使用方法。

4.2 原理设计

通过设定字发生器的数据,使探针依次点亮,形成跑马灯。字信号发生器(Word Generator)可以采用多种方式产生32位同步逻辑信号,用于对数字电路进行测试,是一个通用的数字输入编辑器。

在字信号发生器的左右两侧各有16个端口,分别为0~15和16~31的数字信号输出端,下面的R表示输出端,用以输出与字信号同步的时钟脉冲;T表示输入端,用来接外部触发信号。

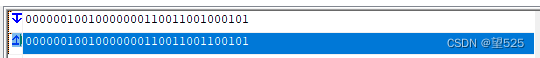

将2的0~15次方依次存入,如下图所示,设置好开始点和终止点,让其循环显示16行数据,从而得到跑马灯效果。将频率设置为100Hz,注意频率不能太快,否则不能人眼无法观察到跑马灯的效果。

4.3 部分结果验证

5 实验4:模拟微程序实现指令

5.1 实验目的

模拟微程序实现机器语言指令。

5.2 原理设计

字发生器的一行输出数据可以作为一条微指令,一条机器语言指令由若干条微指令组成。用字发生器的输出取代实验2中的所有开关,模拟微指令自动执行实现一条机器语言指令。

实验电路图与实验二基本相同,只需要把实验二电路图中的开关全部用字信号发生器的引脚代替即可。

其具体对应引脚如下:

- 0:工作寄存器DR1(HB7)对应的74244(HB2)三态门;

- 1:工作寄存器DR1(HB7)的CLK端;

- 2:工作寄存器DR2(HB8)对应的74244(HB3)三态门;

- 3:工作寄存器DR2(HB8)的CLK端;

- 4:通用寄存器GR1(HB9)的OC端;

- 5:通用寄存器GR1(HB9)的CLK端;

- 6:通用寄存器GR1(HB9)对应的74244(HB5)三态门;

- 7:通用寄存器GR2(HB10)的OC端;

- 8:通用寄存器GR2(HB10)的CLK端;

- 9:通用寄存器GR2(HB10)对应的74244(HB6)三态门;

- 10:8位ALU(HB11)的S0端;

- 11:8位ALU(HB11)的S1端;

- 12:8位ALU(HB11)的S2端;

- 13:8位ALU(HB11)的S3端;

- 14:8位ALU(HB11)的CN端;

- 15:8位ALU(HB11)的M端;

- 16:输入信号的三态门(HB1);

- 17:IN8;

- 18:IN7;

- 19:IN6;

- 20:IN5;

- 21:IN4;

- 22:IN3;

- 23:IN2;

- 24:IN1;

- 25:8位ALU(HB11)对应的74244(HB4)三态门;

-

5.3 部分结果验证