汇编语言与接口技术实验报告——实验一(上)

实验一 算术运算程序设计

一、 实验要求

实验目的:

- 熟练掌握算术运算汇编指令的使用

- 理解有符号数和无符号数运算

- 熟练掌握简单程序设计的基本方法

- 熟练掌握程序的调试方法

实验内容:

- 编程实现两个数:#998877H 和 #778899H 的加法运算。

- 编程实现两个数:#998877H 和 #778899H 的减法运算。

二、 实验设计

1.整体思路

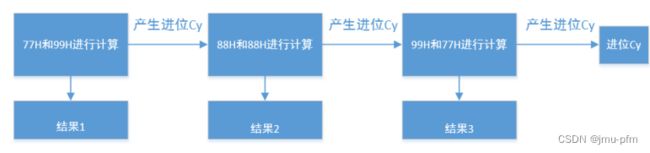

※ 两个数的加法是先从后俩位加法开始计算,逐渐向前计算,同时产生的进位Cy也要一起参与下俩位的加法。

※ 两个数的减法同加法一样,只是公式ADDC换成SUBB。

※ 总体设计思路是分别从NUM1和NUM2中取出数据,进行多次加法操作,并将结果存储在R0、R1、R2中。

2.流程图

图 1-1 算法设计流程图

3.主要模块设计思路及分析

1、定义数据:

在地址NUM1处定义一个2字节的数据,值为9988H。

在地址NUM1处定义一个1字节的数据,值为77H。

在地址NUM2处定义一个3字节的数据,值分别为77H、88H、99H。

2、加法操作:

使用MOV指令将NUM2的地址传给DPTR寄存器,准备从NUM2中取数据。

使用MOV指令将立即数02H传给累加器A,表示接下来要取两个字节的数据。

使用MOVC指令将DPTR基址加上累加器A的变址的结果传给累加器A,这将取得NUM2中的两个字节数据并存储在累加器A中。

使用MOV指令将累加器A的值传给寄存器R0,表示第一个操作数的值。

重复以上步骤,但是将累加器A的值存储在寄存器R1中,表示第二个操作数的值。

再次重复以上步骤,但是将累加器A的值存储在寄存器R2中,表示第三个操作数的值。

3、执行加法操作:

使用MOV指令将NUM2的地址传给DPTR寄存器,准备从NUM2中取数据。

使用MOV指令将立即数01H传给累加器A,表示接下来要取一个字节的数据。

使用MOVC指令将DPTR基址加上累加器A的变址的结果传给累加器A,这将取得NUM2中的一个字节数据并存储在累加器A中。

使用ADDC指令将累加器A与R0相加,将结果存储在A中,同时考虑进位C。

使用MOV指令将A的值传给寄存器R0,表示R0现在存储了第一个操作数的值和第二个操作数的值之和。

重复上述步骤,但是将结果存储在R1中,然后再次重复步骤,将结果存储在R2中。这三次加法操作分别计算了第一个操作数与第二个、第三个操作数的和。

最后,将立即数00H与立即数00H相加,并将结果存储在R3中。这是一次空操作,没有影响寄存器R3的值。

三、 实现效果

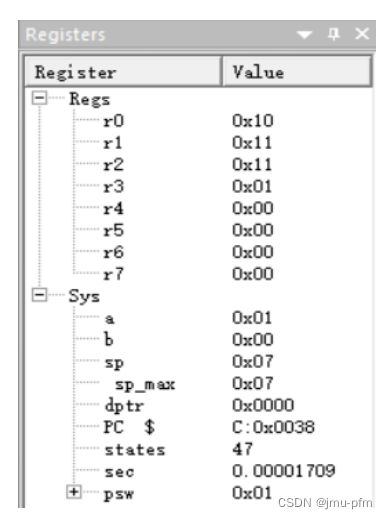

加法:结果分别保存至R0、R1、R2、R3(Cy进位)最终结果是01111110

图 2-1 加法

减法:结果分别保存至R0、R1、R2、R3(Cy进位)最终结果是0021ffde

图 2-2 减法

四、总结

- 进位Cy的最终利用”ADDC A, #00H”实现了A=A+00H+C也就是加上了进位,得到正确结果。

2.运行2个以上的File时会产生错误,内存空间产生重叠,需要移除另一个File。