Verilog VHDL三种建模描述方式——2选1数据选择器

标题Quartus II

标题 Verilog VHDL三种建模描述方式——2选1数据选择器

1,结构化描述方式: 是使用实例化低层次模块的方法,即调用其他已经定义过的低层次模块对整个电路的功能进行描述,或者直接调用Verilog内部预先定义的基本门级元件描述电路的结构。

2,数据流描述方式: 是使用连续赋值语句(assign)对电路的逻辑功能进行描述,该方式特别便于对组合逻辑电路建模。

3,行为级描述方式: 是使用过程块语句结构(always)和比较抽象的高级程序语句对电路的逻辑功能进行描述。

例题:2选1数据选择器

- 结构化描述方式:

代码:

module mux2to1_GL(

a,b,sel,

out

);

input a,b,sel;

output out;

wire nsel,a1,b1; //定义中间变量

not U1(nsel,sel);

and U2(b1,b,nsel);

and U3(a1,a,sel);

or U4(out,a1,b1);

endmodule

步骤:

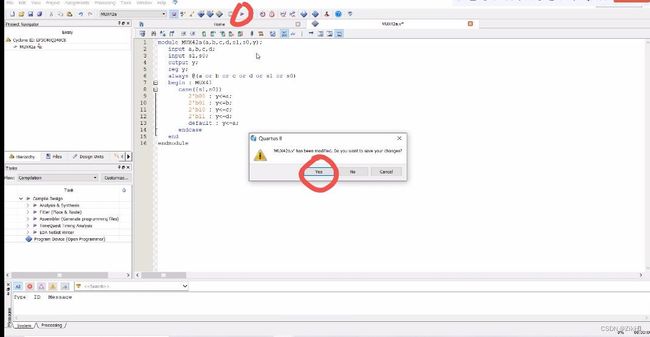

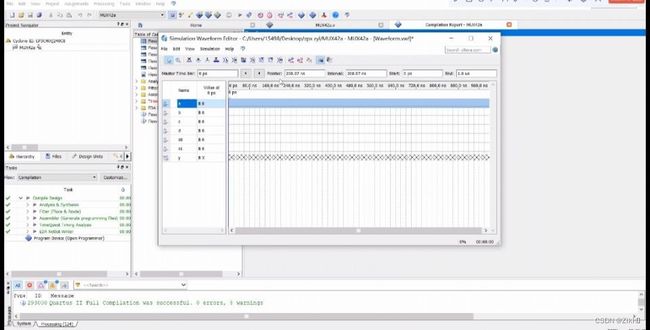

1,在建好一个工程以后,我们点击file>new,然后把代码打上,如图:

2,在点击保存,保存在自己建的文件里。之后运行,如图:

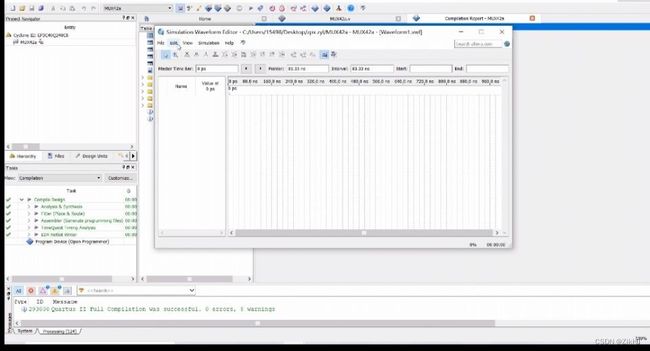

3,接下来就开始仿真,点击file>new>Verification/Debugging File里的University Program VWF,进入仿真,如图:

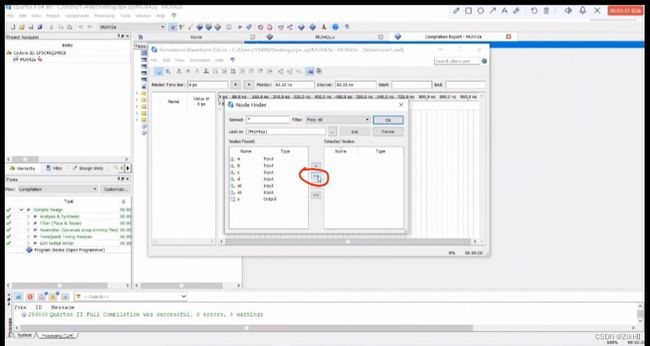

4,在点击Edit>Insert>Insert Node or Bus…>Node Finder…>List旁边三个…>把文件加入过后>list,如图:

5,添加过后,一直点ok,出现如下图:

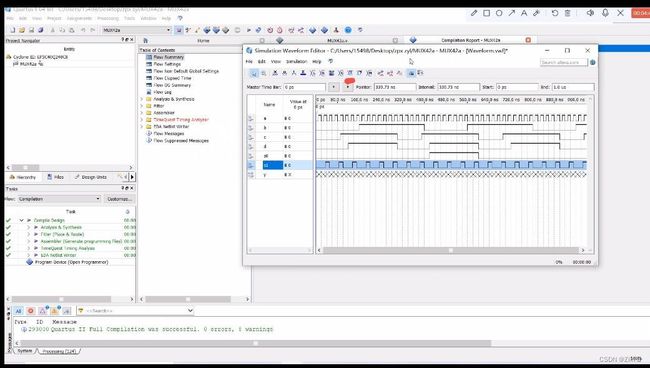

6,点击如下图的红点处的按钮,调整一下相应period和 duty cycle得如下图:

结构体描述就结束了。数据流描述方式和行为描述步骤一样。代码如下:

数据流描述代码:

module Mux2to1_DF(

a,b,sel,

out

);

input a,b,sel;

output out;

assign out = (a&sel) |(b&(~sel)); //out = sel ? a : b;

endmodule

行为描述代码:

module Mux2to1_BH(

a,b,sel,

out

);

input a,b,sel;

output out;

reg out;

always @ (*)

begin

if(sel == 1'b1)

out = a;

else

out = b;

end

endmodule