第三章 存储器系统 ♥

考点1:存储器的层次、类型及特点

1.存储器: cache、内存、外存

内存——存放当前运行的程序和数据。

特点:快,容量小,随机存取, CPU可直接访问。-

通常由半导体存储器构成- [基本原件]

RAM,ROM [型号]

外存——存放能当前使用的程序和数据。-

特点:慢,容量大,顺序存取/块存取。需调入内存后CPU才能访问。-

通常由磁、光存储器构成,也可以由半导体存储器构成-\

磁盘、磁带、CD-ROM、DVD-ROM、固态盘

2,半导体存储器的分类: RAM、 ROM

SRAM特点:

(1)只要不断电,就不会丢失信息;

(2)相对DRAM,存取速度更快。

(3)由触发器构成,集成度较低,功耗大,造价成本高。

(4)一般用作高速缓冲存储器(cache)。

DRAM的特点主要:

(1)相对SRAM,存取速度慢;

(2)由电容构成,集成度高、功耗小,成本低;

(3)适合制作大规模和大容量的内存;

(4)由于电容漏电,数据不能长久保存,需要专门的动态刷新电路,定期给电容补充电荷,即刷新。

RAM的3个特性

(1)可读可写,非破坏性读出,写入时覆盖原内容。

2)随机存取,存取任一单元所需的时间相同。

3)易失性(或挥发性)。当断电后,存储器中的内容立即消失。

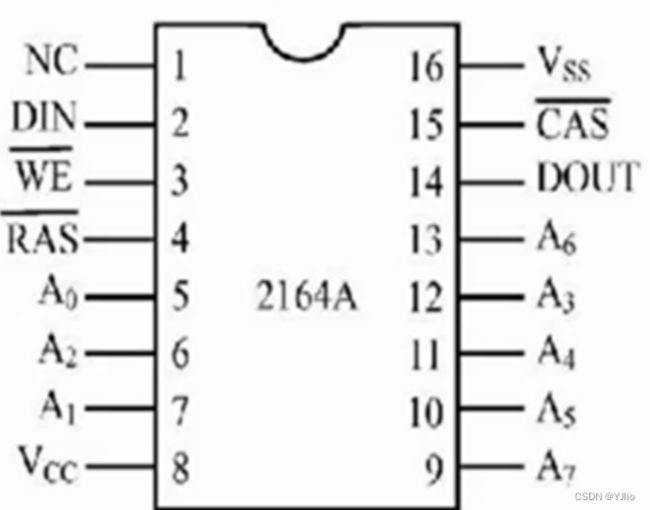

3,静态与动态存储器的构成及其特点,SRAM 6264、 DRAM 2164的引脚构成

静态的WE 是读 OE是写 是分开的

WE 既是读也是写 当是 低电平表示写 高电平 表示读

增加了 RAS 和 CAS 行选线 和 列选线

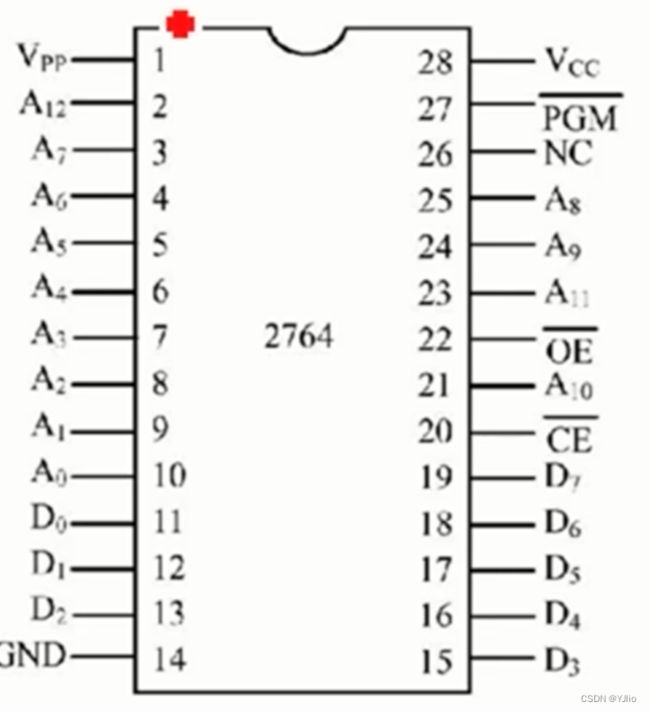

EPROM的2764的引脚构成

只读存储器 OE CE 片选信号线

考点2:主存的容量

1. 概念:

位:bit [32kx8 分解为 32x1024x8 =32kb 32是字数 8是位数]

字节:Byte

字:word 32kx16 [16]

存储元 0/1

存储单元: 8个b 二进制位

存储单元字节编址:

存储单元字 编址:

mov AL.[2000H] #读一个字节

AL=12H

MOV AX,[2000H]

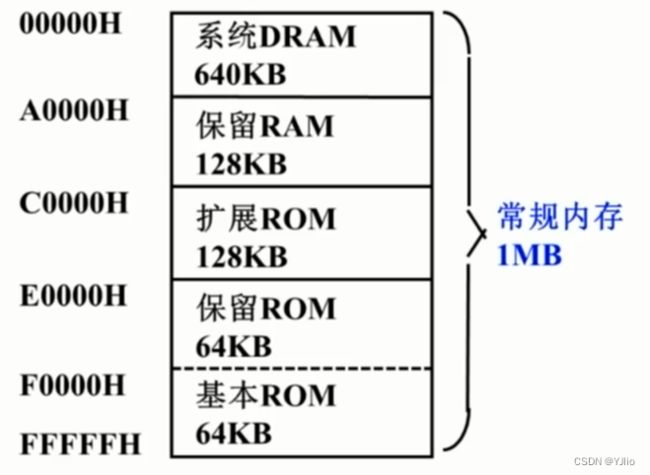

AX=3412H88/86存储空间的分配

8086 是 20位 地址线 访问 1MB

I/O空间的分配

2.容量与地址范围关系

(1) 88/86主存容量1MB

:(2) 中断向量表的1KB:

(3) 1/0接口或主存段的容量64KB:

(4) 6264芯片容量:

8kx8= 8kb

2164:64kx1=

2732: 4kx8

3.芯片容量、地址线、数据线

(1) SRAM 6116有3条控制线,它们是( D )

A. OE、 MREQ、 WE

B. MREQ, CS、 WE

C. OE、 CS、 MREQ

D. OE, CS, WE

SRAM 6264的引脚:

DRAM 2164的引脚:

EPROM 2732的引脚:

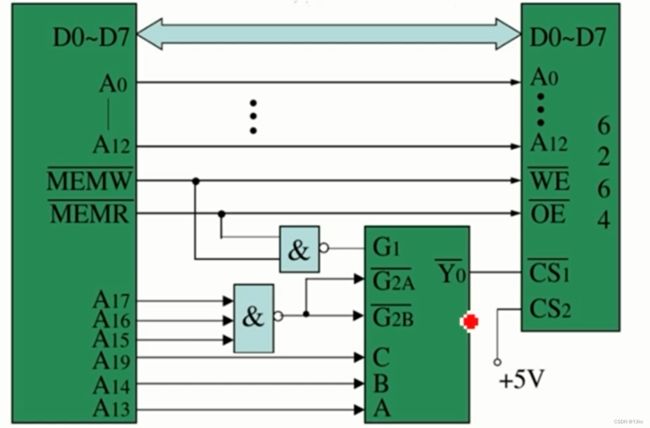

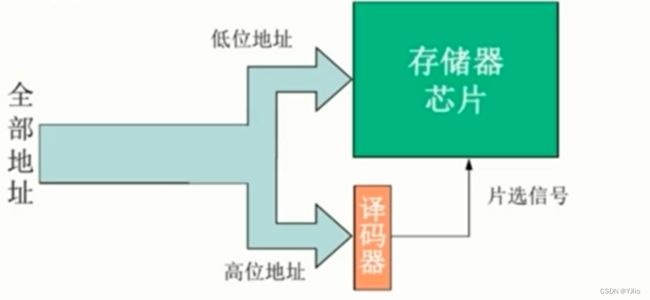

考点3:地址译码方法

1. 译码:

将输入的一组二进制编码变换为一个特定的控制信号,即:将输入的一组高位地址信号通过变换,产生一个有效的控制信号,用于选中某一个存储器芯片,从而确定该存储器芯片在内存中的地址范围。

2. 译码器

三个输入端 C B A

三个使能端

CE片选信号

| A | B | C | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

| --- | --- | --- | --- | --- | --- | --- | --- | --- | --- | --- |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

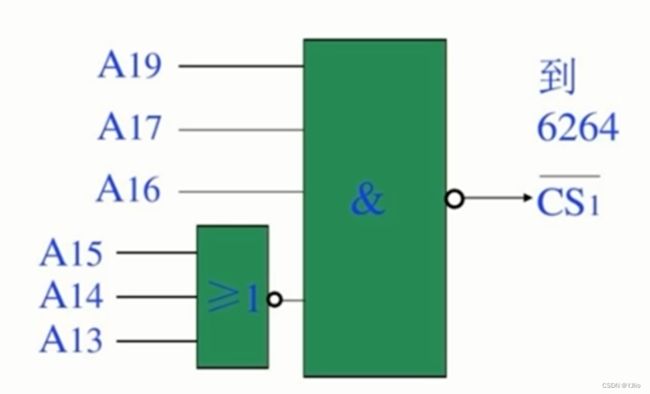

3. 部分译码

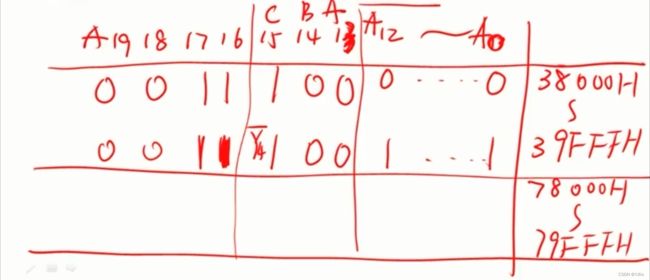

将SRAM 6264芯片与系统连接,使其地址范围为: 38000H-39FFFH和78000H-79FFFH.

选择使用74LS138译码器构成译码电路

6464 8kx8 =2^13x8 13根片内地址线

全译码

用全部的高位地址信号作为译码信号,使得存储器芯片的每一个单元都占据一个唯一的内存地址。