集成电路总线(Inter-Integrated Circuit, I2C)

目录

- 1. 半双工 串行 同步

-

- 波特率

- 2. 一主多从传输

-

- START 与 STOP

- Byte format 与 Acknowledge

- 7bit寻址传输协议

- 10bit寻址传输协议

- 通用广播传输协议

- 3. 多主多从传输

-

- SCL同步 与 SDA仲裁

《 I2C-bus specification and user manual UM10204—4 April 2014》

《DesignWare DW_apb_i2c Databook - Synopsys》

I2C详解(一)

【数字IC】深入浅出理解I2C协议

I2C协议靠这16张图彻底搞懂(超详细)

I2C通信详解介绍(初学,浅显易懂,基本知识)

IIC、SPI、UART、USART、USB、CAN等通讯协议原理及区别

常用通信协议——IIC详解(全网最全)

多路数据整形器(Multi Channel Data Formatter, MCDF)功能描述

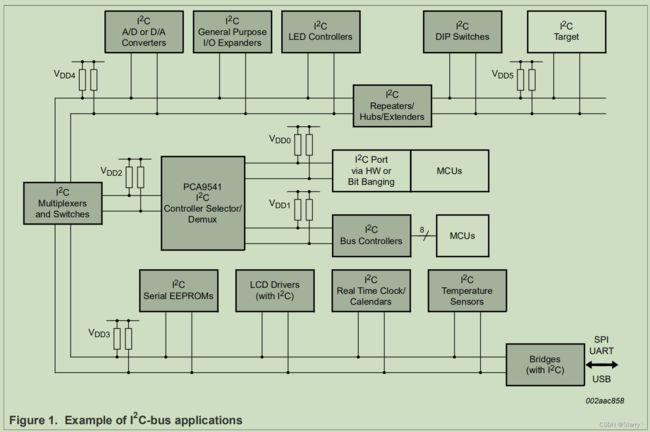

集成电路总线(Inter-Integrated Circuit,I2C),仅由双向两条线构成,属半双工、串行、同步通信总线,可使用多主多从架构,是由飞利浦公司在1980年代初设计。

方便了主板、嵌入式系统或手机与周边设备组件之间的低速通讯。由于其简单性,它被广泛用于微控制器与传感器阵列,显示器,IoT设备,EEPROM,ADC/DAC等多种微处理器之间的通信。

1. 半双工 串行 同步

I2C总线只由SDA和SCL两根线构成,一个串行数据线、一个串行时钟线,其中SDA是双向的,因此可实现master和slave之间的数据半双工收发。

半双工,即要么发送、要么接受,一根输入输出线SDA即可

同时I2C是基于地址对slave和其内部的寄存器进行寻址,注意这一点与SPI不同(SPI是csn片选信号),因此I2C扩展性极强,可实现多主多从的架构,同时主从器件数量只取决于总线的电气容量。

不仅如此,I2C的数据传输具备应答功能,每次数据传输,接收方都可返回一个ACK信号。

当有多个master设备想要访问同一个slave,I2C也具备仲裁的功能

波特率

I2C也是基于同步时钟进行数据传输的,传输速度有不同的模式

双向传输:

● 标准模式(Standard-mode) :高达100 Kbps

● 快速模式(Fast-mode) :高达400 Kbps

● 快速模式+(Fast-mode Plus) :高达1 Mbps

● 高速模式(High-speed mode) :高达3.4 Mbps

单向传输:

● 超快速模式(Ultra Fast-mode):高达5M bps

2. 一主多从传输

单个master时,master在sda上串行驱动slave的地址信息和控制信息,以完成对选定slave的读写

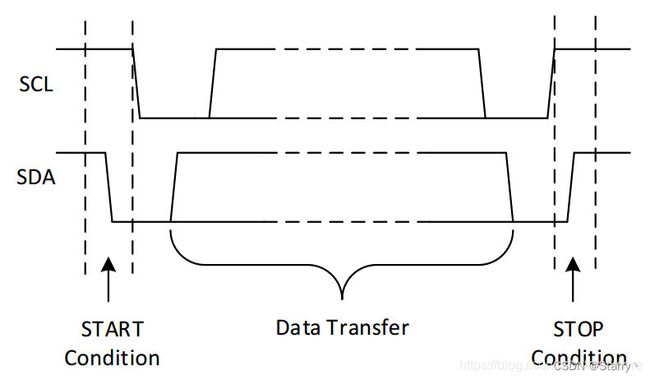

START 与 STOP

即传输开始条件和传输终止条件

注意初始时SCL和SDA均为高电平

● START: 由master发起,SCL为高,SDA由高拉低,表示传输开始

● STOP: 由master发起,SCL为高,SDA由低拉高,表示传输终止

发起START后开始数据传输,在此期间master还可以再发一次START以重新开始新的传输

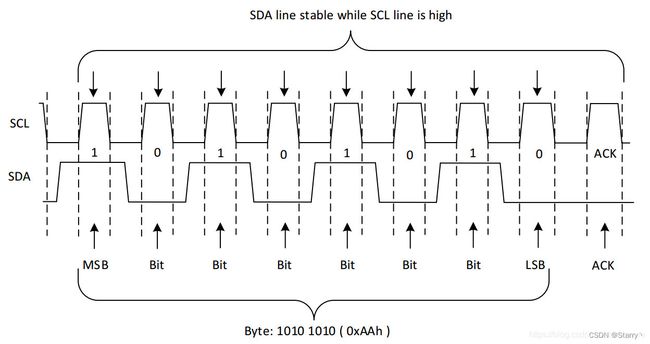

Byte format 与 Acknowledge

开始传输后,master和slave之间的数据传输是以每1byte+1个ACK应答为单位。

首先,I2C协议要求SDA只可在SCL为低时变化,在SCL为高时必须保持,可以看作是SDA有效标志

然后就是数据格式,共9bit

● 8bit 数据位: 每次传输只能传输8bit数据体,且是先MSB后LSB。

● 1bit 响应位: 1byte数据位传输完成之后,发送方释放SDA,在第9个高电平处接收方需反馈一个响应位,低电平为ACK表示确认收到数据,高电平为NACK表示slave接受失败或者master接受读数据结束。

注意发送方释放sda后改由接收方驱动sda,默认驱动高电平,确认接受成功后接收方会驱动低电平。

为保证最后1bit能够顺利传输,发送方必须在第8个高电平和第9个高电平之间的那个低电平释放sda。

7bit寻址传输协议

当master向某个特定的slave发出读写请求的时候,就需要按照一定的时序与slave握手。

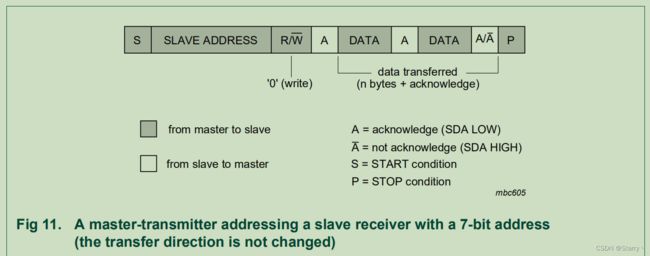

● master写slave

第一次传输,master发送7bit地址用于片选slave,最后1bit为0表示写操作,需要slave反馈ACK

7bit寻址理论上一个master可以寻址128个slave,但是有16个7bit地址有特殊含义,而且还要求总线总电容≤400pF,这两个条件约束了slave的接入数目

第二次传输,master发送8bit寄存器地址用于选择特定slave内部的哪个寄存器,需要slave反馈ACK

第三次传输,master发送要写入的8bit数据,需要slave反馈ACK

第四次传输,master发送要写入的8bit数据,需要slave反馈ACK

…

或者一次传输就直接选定slave地址也行

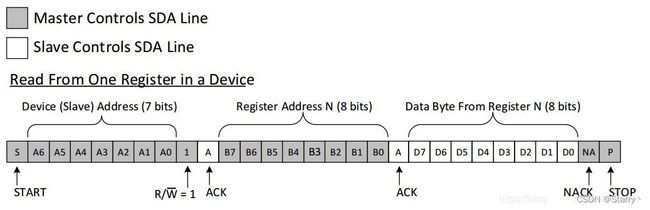

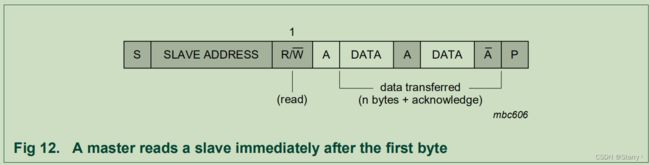

● master读slave

第一次传输,master发送7bit地址用于片选slave,最后1bit为1表示读操作,需要slave反馈ACK

第二次传输,master发送8bit寄存器地址用于选择特定slave内部的哪个寄存器,需要slave反馈ACK

第三次传输,slave发送读出的8bit数据,master反馈ACK

第四次传输,slave发送读出的8bit数据,master反馈ACK

…

第n次传输,slave发送读出的8bit数据,master反馈NACK停止当前传输,下一拍master发送START或STOP

或者一次传输就直接选定slave地址也行

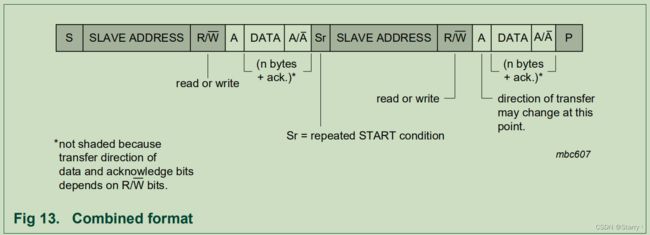

● master在STOP前多次读写

即STOP之前对多个地址进行读写操作。这就需要在对一个地址读写完成后,重新发一个START,继续对别的地址进行操作。

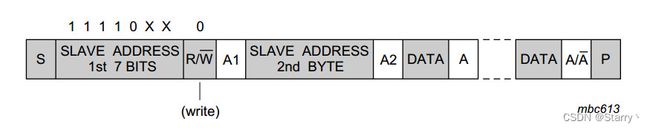

10bit寻址传输协议

10bit寻址与7bit类似,并不常用。

● master写slave

第一次传输,master发送111_10XX,此处XX表示slave地址的高2bit,最后1bit为0表示写操作。所有地址高2bit为XX的slave都会反馈ACK

第二次传输,master发送低8bit的slave地址,需要slave反馈ACK

第三次传输,master发送要写入的8bit数据,需要slave反馈ACK

第四次传输,master发送要写入的8bit数据,需要slave反馈ACK

…

● master读slave

第一次传输,master发送1111_0XX0,此处XX表示slave地址的高2bit。所有地址高2bit为XX的slave都会反馈ACK

第二次传输,master发送低8bit的slave地址,需要slave反馈ACK

第三次传输,master发送START,并重新发送1111_0XX1,最后1bit为1表示读,需要slave确认并反馈ACK

第四次传输,slave发送读出的8bit数据,master反馈ACK

…

第n次传输,slave发送读出的8bit数据,master反馈NACK停止当前传输,下一拍master发送START或STOP

注意第一次发1111_0XX0,第二次发的是1111_0XX1,前两次传输与master写slave前两次传输完全相同,并不是很理解原因,给出原文:

Controller-receiver reads target-transmitter with a 10-bit target address. The transfer

direction is changed after the second R/W bit (Figure 15). Up to and including

acknowledge bit A2, the procedure is the same as that described for a controller-transmitter addressing a target-receiver. After the repeated START condition (Sr), a

matching target remembers that it was addressed before. This target then checks if the

first seven bits of the first byte of the target address following Sr are the same as they

were after the START condition (S), and tests if the eighth (R/W) bit is 1. If there is a

match, the target considers that it has been addressed as a transmitter and generates

acknowledge A3. The target-transmitter remains addressed until it receives a STOP condition § or until it receives another repeated START condition (Sr) followed by a different target address.

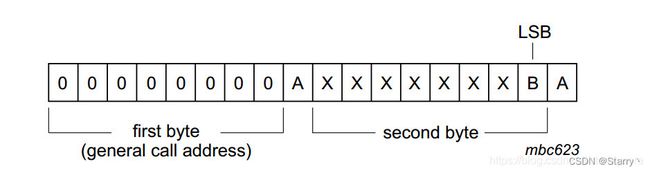

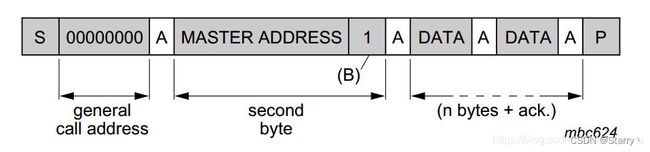

通用广播传输协议

指当master要向总线上所有的slave都进行访问时的传输协议。该协议下master发送的数据会发送给所有的slave,而master接受的ACK信息则是每个slave反馈的ACK信息线与的结果。

格式如下

● first byte:8’b0000_0000、second byte:8’b0000_0110

第一个byte表示通用广播地址,告知所有的slave要读取后面的byte。第二个byte表示所有的slave复位并将接下来发的每个byte写入slave内部可写寄存器。

● first byte:8’b0000_0000、second byte:8’b0000_0100

第一个byte表示通用广播地址,告知所有的slave要读取后面的byte。第二个byte表示将接下来发的每个byte写入slave内部可写寄存器,不复位

● first byte:8’b0000_0000、second byte:8’bXXXX_XXX1

第一个byte表示通用广播地址,告知所有的slave要读取后面的byte。第二个byte中高7bit为master地址,即master广播自身的地址,所有slave通过检测master地址来判断是否将接下来的数据写入自己内部的寄存器内。

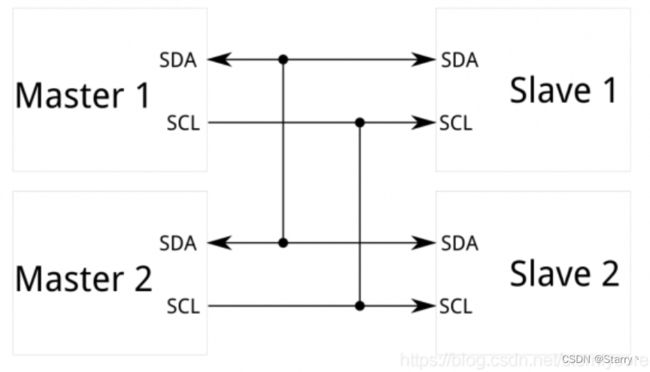

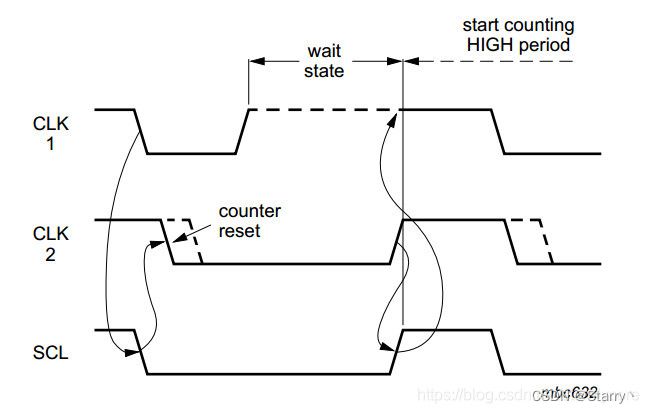

3. 多主多从传输

当有多个master参与数据传输,就需要对时钟和数据进行仲裁

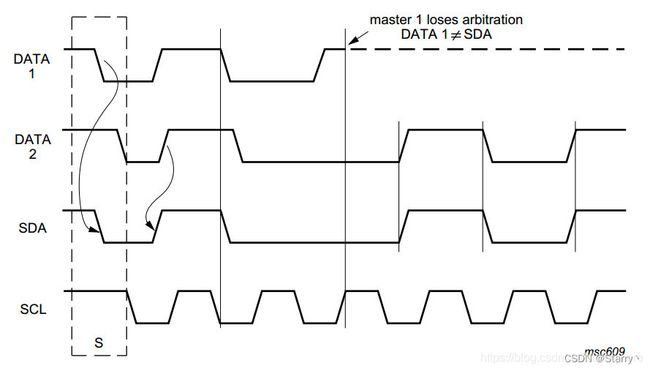

SCL同步 与 SDA仲裁

● 时钟同步: I2C总线输入给每个slave的SCL其实是每个master发出的SCL线与的结果。

● 数据仲裁: 与时钟同步意思一样,I2C总线输入给每个slave的SDA其实是每个master发出的SDA线与的结果。

而且在SCL为高时,每个master检测SDA与自己的发出的SDA是否一致,如果一致则继续传输,否则认为自己失掉仲裁恒输出高电平

所以每个master还需要输入线与后的SCL和SDA