FPGA的斐波那契数列Fibonacci设计verilog,代码和视频

名称:斐波那契数列Fibonacci设计verilog

软件:Quartus

语言:Verilog

代码功能:

设计一个产生斐波那契数列(也叫黄金分割数列)的硬件电路:

斐波那契数列中每个数为其相邻前两个数的和:即FN=FN1+FN2,(数列的前两个数F和F均为1)

(1)基本要求

根据不同输入N(>=3),产生FN最大为32位,在新的F产生出来前,N将维持不变;F应保持不变直到N又发生变化

2画出设计结构图:数据通路和控制通路、控制策略

3写出该设计的 Verilog描述

(2)扩展功能

随机生成指定范围内的N整数,并计算斐波那契数列F产生次数。

本代码支持使用modelsim仿真和quartus仿真

modelsim仿真演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=211

quartus仿真演示视频:

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=211

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

斐波那契数列Fibonacci设计verilog(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:设计一个产生斐波那契数列(也叫黄金分割数列)的硬件电路:斐波那契数列中每个数为其相邻前两个数的和:即FN=FN1+FN2,(数列的前两个数F和F均为1) (1)基本要求 根据不同输入N(>=3),产生FN最大为32位,在新的F产生出来前,N将维持不变;F应保持不变直到名称:斐波那契数列Fibonacci设计verilog(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:设计一个产生斐波那契数列(也叫黄金分割数列)的硬件电路:斐波那契数列中每个数为其相邻前两个数的和:即FN=FN1+FN2,(数列的前两个数F和F均为1) (1)基本要求 根据不同输入N(>=3),产生FN最大为32位,在新的F产生出来前,N将维持不变;F应保持不变直到![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=211

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=211

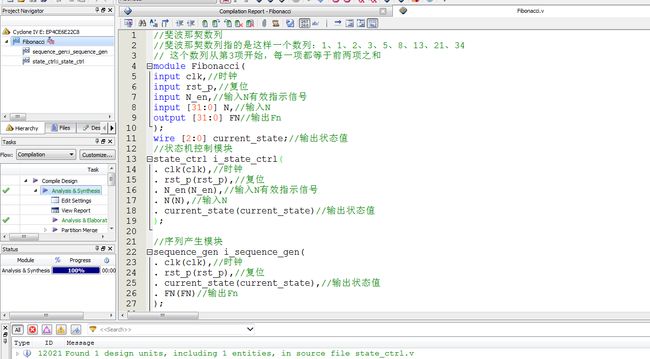

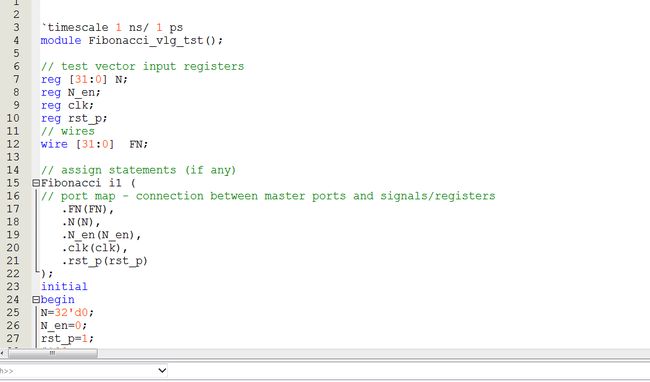

部分代码展示

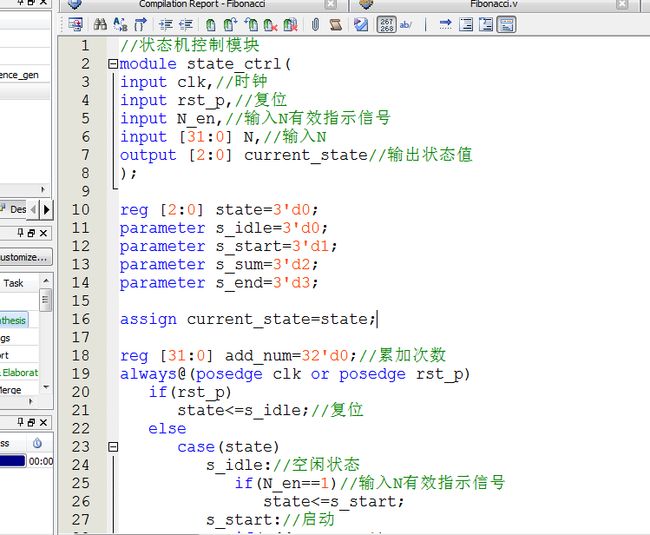

//斐波那契数列 //斐波那契数列指的是这样一个数列:1、1、2、3、5、8、13、21、34 // 这个数列从第3项开始,每一项都等于前两项之和 module Fibonacci( input clk,//时钟 input rst_p,//复位 input N_en,//输入N有效指示信号 input [31:0] N,//输入N output [31:0] FN//输出Fn ); wire [2:0] current_state;//输出状态值 //状态机控制模块 state_ctrl i_state_ctrl( . clk(clk),//时钟 . rst_p(rst_p),//复位 . N_en(N_en),//输入N有效指示信号 . N(N),//输入N . current_state(current_state)//输出状态值 ); //序列产生模块 sequence_gen i_sequence_gen( . clk(clk),//时钟 . rst_p(rst_p),//复位 . current_state(current_state),//输出状态值 . FN(FN)//输出Fn ); endmodule //序列产生模块 module sequence_gen( input clk,//时钟 input rst_p,//复位 input [2:0] current_state,//输出状态值 output reg [31:0] FN//输出Fn ); parameter s_idle=3'd0; parameter s_start=3'd1; parameter s_sum=3'd2; parameter s_end=3'd3; //数列计算 reg [31:0] Fib_sequence=32'd1; reg [31:0] Fib_sequence_delay=32'd1; always@(posedge clk) if(rst_p) Fib_sequence<=32'd1; else if(current_state==s_sum)//累加状态下 begin Fib_sequence_delay<=Fib_sequence;//缓存前一个数到Fib_sequence_delay Fib_sequence<=Fib_sequence+Fib_sequence_delay;//前两项之和 end else if(current_state==s_end)begin//结束 Fib_sequence<=32'd1; Fib_sequence_delay<=32'd1; end

设计文档:

设计文档.doc

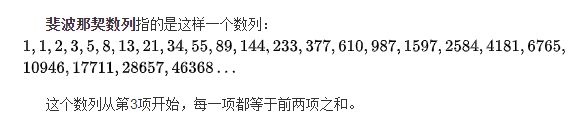

1. 数列

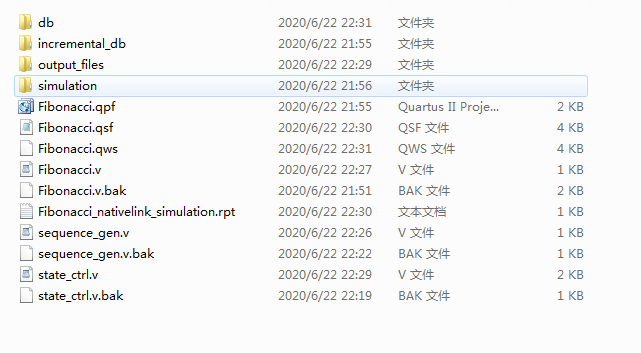

2. 工程文件

3. 程序文件

4. 程序编译

5. RTL图

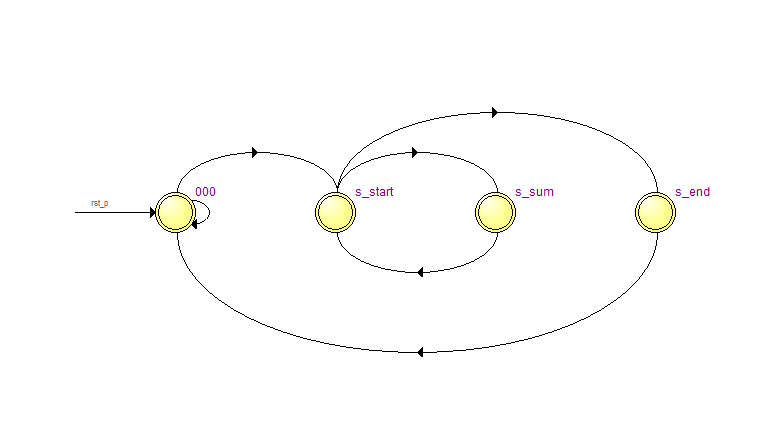

状态机视图

6. Testbench

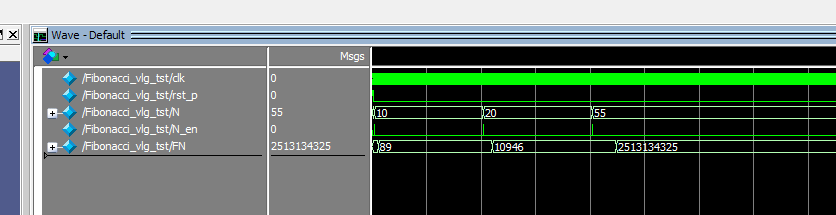

7. 仿真图

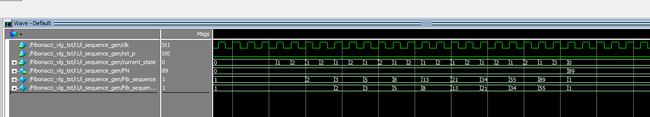

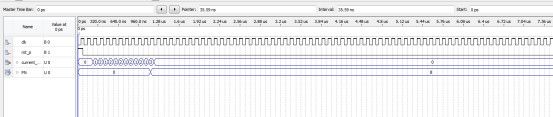

整体仿真图

数列第0个为1,第1个为1,第2个为2.。。。。第10个为89,第20个为10946。。。

可以看到仿真图第10个为89,第20个为10946正确。

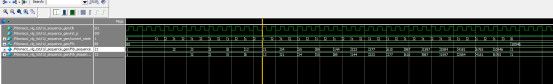

状态机控制模块

数列产生模块

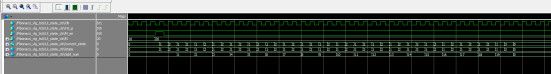

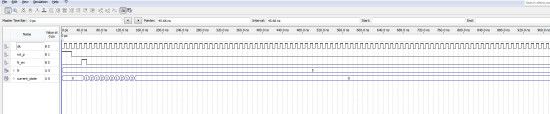

quarttusII自带仿真

整体仿真

数列第0个为1,第1个为1,第2个为2.。。。。第5个为8,第20个为10946。。。

可以看到仿真图第5个为8,第20个为10946正确。

状态控制模块

数列产生模块