【Verilog】组合逻辑(多路选择器设计)

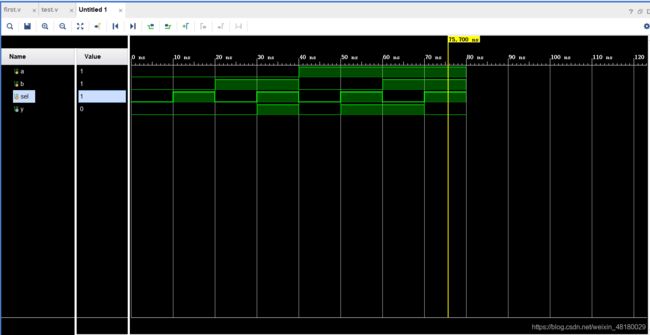

module fn_sw(

A,

B,

sel,

Y

);

input A;

input B;

input sel;

output Y;

assign Y = sel ? (A^B) :(A&B);

endmodule

module fn_sw(

A,

B,

sel,

Y

);

input A;

input B;

input sel;

output Y;

reg Y;

always@(A or B or sel)//是所有的输入信号

begin

if(sel == 1)begin

Y <= A ^ B;

end

else begin

Y <= A & B;

end

end

endmodule

module test(

);

reg a,b,sel;

wire y;

fn_sw f(.A(a),.B(b),.sel(sel),.Y(y));

initial begin // 按时间定义变量的值

a <= 0;b <= 0;sel <= 0;

#10 a <= 0;b <= 0;sel <= 1;

#10 a <= 0;b <= 1;sel <= 0;

#10 a <= 0;b <= 1;sel <= 1;

#10 a <= 1;b <= 0;sel <= 0;

#10 a <= 1;b <= 0;sel <= 1;

#10 a <= 1;b <= 1;sel <= 0;

#10 a <= 1;b <= 1;sel <= 1;

#10 $stop;

end

endmodule

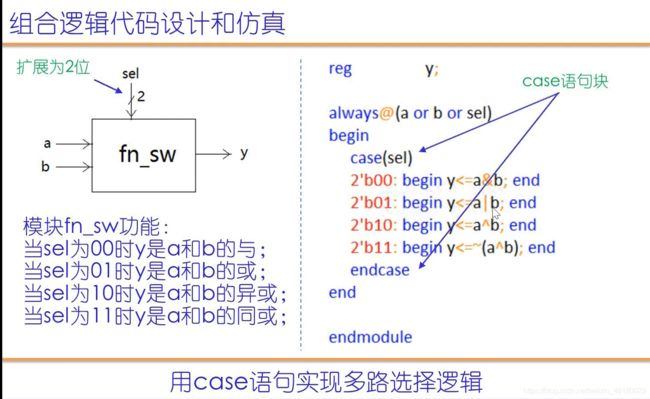

module fn_sw_4(

A,

B,

sel,

Y

);

input A;

input B;

input[1:0] sel;

output Y;

reg Y;

always@(A or B or sel)//是所有的输入信号

begin

case(sel)

2'b00 : begin Y <= A & B;end

2'b01 : begin Y <= A | B;end

2'b10 : begin Y <= A ^ B;end

2'b11 : begin Y <= ~(A ^ B);end

endcase

end

endmodule

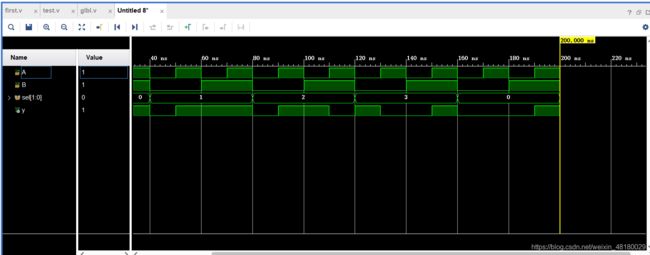

module test(

);

reg a,b,sel;

wire y;

fn_sw_4 f(.A(a),.B(b),.sel(sel),.Y(y));

initial begin // 按时间定义变量的值

a <= 0;b <= 0;sel <= 2'b00;

#10 a <= 0;b <= 1;sel <= 2'b00;

#10 a <= 1;b <= 0;sel <= 2'b00;

#10 a <= 1;b <= 1;sel <= 2'b00;

#10 a <= 0;b <= 0;sel <= 2'b01;

#10 a <= 0;b <= 1;sel <= 2'b01;

#10 a <= 1;b <= 0;sel <= 2'b01;

#10 a <= 1;b <= 1;sel <= 2'b01;

#10 a <= 0;b <= 0;sel <= 2'b10;

#10 a <= 0;b <= 1;sel <= 2'b10;

#10 a <= 1;b <= 0;sel <= 2'b10;

#10 a <= 1;b <= 1;sel <= 2'b10;

#10 a <= 0;b <= 0;sel <= 2'b11;

#10 a <= 0;b <= 1;sel <= 2'b11;

#10 a <= 1;b <= 0;sel <= 2'b11;

#10 a <= 1;b <= 1;sel <= 2'b11;

#10 $stop;

end

endmodule

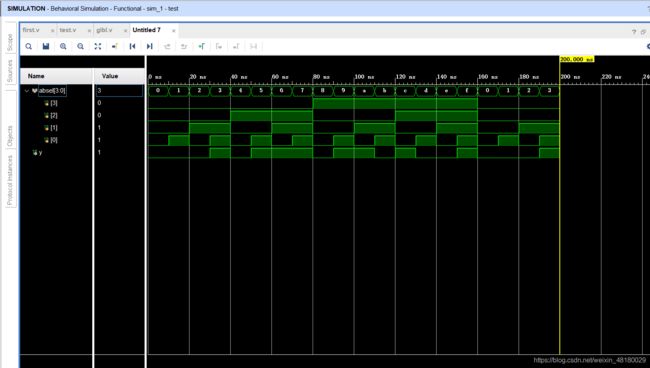

module test(

);

reg[3:0] absel;

wire y;

fn_sw_4 f(.A(absel[0]),.B(absel[1]),.sel(absel[3:2]),.Y(y));

initial begin // 按时间定义变量的值

absel <= 0;

#200 $stop;

end

always #10 absel <= absel + 1;

endmodule

在功能模块中,输入端口只能是wire型

当输出端口信号需要在always语句中被赋值,类型选择reg型。

在测试模块中,在initial中,需要被赋值的信号数据类型设为reg型

只要输出显示的信号,数据类型可以设为wire型。