NOR FLASH读、写、擦原理与实现(1)——性能简述与术语解释

这段时间,由于项目需要,我得对FLASH的运作原理做初步的理解,并且对其实现方法进行研究。我将通过几篇博客将我的学习历程记录下来,并且希望跟诸位有缘看到博客的人共同讨论、学习。以下笔记将以芯片“N25Q00AA”为研究对象。不能只是做知识的简单重复与记忆,一定要应用在实际的项目中。

一、设备简述

1、NOR FLASH的存储架构是怎样的?以“N25Q00AA”为例

NOR FLASH(1*1Gb) -->

Die(4*256Mb) --> 可擦

Segment(2*128Mb) -->

Sector(512*64KB) --> 可擦、写保护

Subsector(16*4KB) --> 可擦

Page(16*256Bytes) --> 不可擦、可编程

Byte(32*8Bit)

2、NOR FLASH的最小访问单元?

是8-BIT模式或16-BIT模式?或者是可选择的?项目中使用的8-BIT模式。目前还没有在芯片手册中找到关于芯片“N25Q00AA”是8-BIT模式或16-BIT模式的描述。

3、NOR FLSAH的写操作具有怎样的特点?

(1)写操作需要遵循特定的命令序列,最终由芯片内部的控制单元完成写操作;

(2)通常需要先擦除再执行写操作。原因:因为在对FLASH进行写操作的时候,每个BIT可以由1变为0,但不可以由0修改为1。故,为了保证写操作的正确性,在进行写操作前,都要执行擦除操作。擦除操作会将FLASH的一个SECTOR/BANK/整片FLASH的值全部修改为0xFF。如此一来,写操作就可以正确执行了。

4、通信协议

(1)单SPI(Extended SPI)

(2)双SPI(Dual I/O SPI)

(3)四SPI(Quad I/O SPI)

在我们的项目中使用的是哪种通信协议呢?

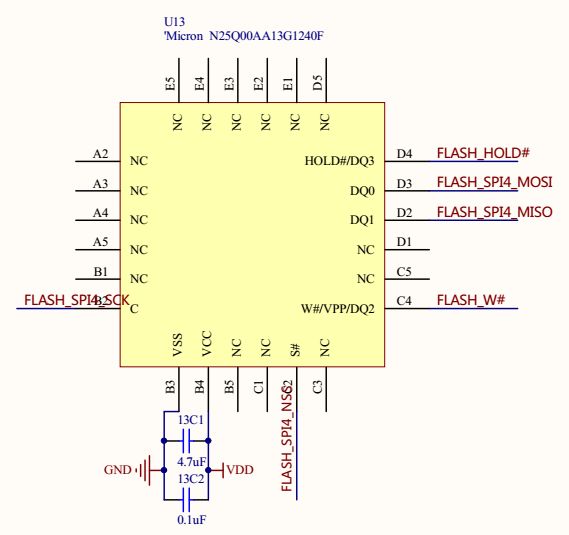

5、引脚描述

C: CLOCK , 提供时钟,出现在串行总线上的命令、地址、或者数据会在时钟上升沿被锁住。数据将在下降沿被移除。

S#: 片选信号,低电平有效,开启后,S#,需要一个下降沿,这个下降沿是在发送任何命令之前就得有的。高电平取消选定,DQ1为高阻。

RESET#:当RESET为高时,内存是正常工作的模式,当RESET为低时,有效,内存进入reset模式。

HOLD#: 中止任何串行通信。DQ1为高阻状态,要开启HOLD之前,片选要置低。低电平有效。

W#:写保护,when in extended SPI with single or dual commands, the WRITE PROTECT function is selectable by the voltage range applied to the signal.

低电平时,信号作为一个写保护控制输入,内存防止被擦除/写入。低电平有效。

DQ0:输入口,输入与IO口可以接收命令、地址、和数据。上升沿至时其值将被锁住。当用作输出时,数据在下降沿移出。

DQ1:输出口,下降沿时钟,数据被输出。当用作输入时,数据在上升沿锁住。

DQ2:当使用了QIO-SPI模式,or ,extended SPI模式使用QUAD FAST READ 命令,DQ2用来提供输入与输出。

DQ3:当使用了quad SPI 模式,or ,extended SPI 模式使用quad FAST READ 命令,DQ3提供了输入与输出。

6、无本地坏区管理

可通过软件的方式解决。

二、术语解释

1、芯片内执行(XIP,eXecute In Place)

依据“N25Q00AA”芯片手册翻译如下:片内执行模式使得,可以通过向存储设备发送地址的方式读取存储内容,输出将在1、2或4个并行的引脚输出(这一点取决于用户需求)。XIP模式给实际应用听了极大地灵活性、节省了命令开支、减少了随机存取时间。

说白了,就是芯片内部嵌入的算法完成对芯片的操作。

2、一次性可编程区域(OTP)

64字节

3、双倍传输率(DTR)

下一篇将会讨论NOR FLASH的读、写、擦的原理及时序。